Tabla de contenido:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:41.

- Última modificación 2025-01-23 14:39.

En esta guía vamos a construir y controlar un sistema de atenuación LED externo. Con los botones disponibles, el usuario puede atenuar la bombilla LED a cualquier brillo deseado. El sistema utiliza la placa Basys 3 y está conectada a una placa que contiene una resistencia y la bombilla LED. Al presionar el botón "arriba" designado aumentará el brillo, y al presionar el botón "abajo" disminuirá el brillo hasta cero. Esto no solo evita que el usuario quede cegado por bombillas brillantes como el sol, sino que también ahorra energía.

Paso 1: crear contador de entrada

Para este paso creamos el componente que determina el nivel de brillo (a través de un reloj) usando dos interruptores: uno para aumentar y otro para disminuir. Utilizando VHDL, producimos el contador mediante el uso de flip-flops D. Al presionar el botón "arriba" empuja el siguiente estado al estado actual, dando salida a la pantalla de siete segmentos y la bombilla LED.

entidad updown_counter es

Puerto (present_state: out STD_LOGIC_VECTOR (3 abajo a 0); estado_anterior: en STD_LOGIC_VECTOR (3 abajo a 0); next_state: en STD_LOGIC_VECTOR (3 abajo a 0); clk: en STD_LOGIC; down_enable: en STD_LOGIC: en arriba; end updown_counter; arquitectura El comportamiento de updown_counter es begin flop: process (next_state, clk, up_enable, down_enable, previous_state) begin if (rising_edge (clk)) then if (up_enable = '1' and not (next_state = "0000")) then present_state <= next_state; elsif (down_enable = '1' y no (previous_state = "1111")) luego present_state <= previous_state; terminara si; terminara si; fracaso del proceso de finalización; end Behavioral;

También necesitamos un reloj para cada entrada a la que se enganche (cuando sube), por lo que también creamos un divisor de reloj que determina qué tan rápido se pueden presionar los botones entre cada nivel de brillo. Este divisor de reloj nos permite mostrar correctamente el nivel correcto en la pantalla de siete segmentos y producir el nivel correcto de intensidad para cada nivel.

entidad counter_clkDiv es

Puerto (clk: en std_logic; sclk: fuera de std_logic); end counter_clkDiv; arquitectura my_clk_div de counter_clkDiv es constante max_count: integer: = (10000000); señal tmp_clk: std_logic: = '0'; begin my_div: process (clk, tmp_clk) variable div_cnt: integer: = 0; empezar si (aumento_de_borde (clk)) entonces si (div_cnt> = MAX_COUNT) entonces tmp_clk <= no tmp_clk; div_cnt: = 0; más div_cnt: = div_cnt + 1; terminara si; terminara si; sclk <= tmp_clk; finalizar el proceso my_div; end my_clk_div;

Paso 2: Cree un divisor de reloj LED

Para este paso creamos un divisor de reloj para la bombilla LED para determinar 16 niveles diferentes de intensidad. Con 0 estando apagado a 15 mostrando el brillo máximo, el divisor del reloj incrementa cada botón presionado por lo que configuramos como los niveles de brillo. Cada nivel creciente significó un aumento en el reloj de la bombilla LED. Recordando que el brillo no aumenta linealmente, pusimos el reloj al máximo que podía ir y disminuimos nuestros relojes en consecuencia.

Nota: estamos usando un LED azul. El uso de un color diferente (como el rojo) requerirá relojes ligeramente diferentes por completo; una configuración de brillo medio para el azul ya podría ser el brillo máximo para el rojo. Esto sucede porque diferentes longitudes de onda de luz requerirán diferentes cantidades de energía, y los colores más fríos como el púrpura y el azul requieren más energía, mientras que los colores más cálidos como el rojo y el naranja requieren menos energía.

la entidad led_clkDiv es Puerto (present_state: en STD_LOGIC_VECTOR (3 downto 0); clk: en STD_LOGIC; led_clk: out STD_LOGIC); end led_clkDiv; arquitectura El comportamiento de led_clkDiv es la señal tmp_clk: std_logic: = '0'; variable compartida max_count: integer; begin count_stuff: process (present_state) begin case present_state es cuando "0000" => max_count: = 0; cuando "0001" => max_count: = 2; cuando "0010" => max_count: = 4; cuando "0011" => max_count: = 6; cuando "0100" => max_count: = 8; cuando "0101" => max_count: = 10; cuando "0110" => max_count: = 12; cuando "0111" => max_count: = 14; cuando "1000" => max_count: = 16; cuando "1001" => max_count: = 25; cuando "1010" => max_count: = 50; cuando "1011" => max_count: = 100; cuando "1100" => max_count: = 150; cuando "1101" => max_count: = 200; cuando "1110" => max_count: = 250; cuando "1111" => max_count: = 300; caso final; finalizar el proceso count_stuff; my_div: process (clk, tmp_clk, present_state) variable div_cnt: integer: = 0; comenzar si (aumento_de_borde (clk)) luego si (div_cnt> = max_count) entonces tmp_clk <= no tmp_clk; div_cnt: = 0; más div_cnt: = div_cnt + 1; terminara si; terminara si; led_clk <= tmp_clk; finalizar el proceso my_div; end Behavioral;

Paso 3: creación del controlador LED

Ahora que hemos llegado hasta aquí, es hora de combinar finalmente todos los componentes que hemos creado hasta ahora en el archivo del controlador LED.

En resumen, los componentes utilizados son los siguientes:

- Contador de entrada (updown_counter)

- Divisor de reloj (counter_clkDiv)

- Divisor de reloj LED (led_clkDiv)

- Controlador de pantalla de siete segmentos (sseg_dec) (archivo adjunto)

El controlador de pantalla de siete segmentos en realidad no se discutió anteriormente porque en realidad tomamos prestado el archivo VHDL del Dr. Bryan Mealy debido a su código largo y complicado. Lo que esencialmente hace es conducir nuestras entradas de botón a la pantalla de siete segmentos en la placa Basys 3 para que sepamos en qué nivel de brillo.

En el futuro, el controlador LED usa flip flops para aumentar o disminuir el recuento que controla tanto la pantalla de siete segmentos como el nivel de brillo de la bombilla LED simultáneamente.

el contador de entidad es Port (clk: en STD_LOGIC; up_enable: en STD_LOGIC; down_enable: en STD_LOGIC; SEGMENTOS: out STD_LOGIC_VECTOR (7 hacia abajo 0); DISP_EN: hacia fuera STD_LOGIC_VECTOR (3 hacia abajo 0); led_LOGIC: hacia fuera STD_VECTOR; contador de finalización; arquitectura El comportamiento del contador es el componente updown_counter es Port (present_state: out STD_LOGIC_VECTOR (3 downto 0); previous_state: in STD_LOGIC_VECTOR (3 downto 0); next_state: in STD_LOGIC_VECTOR (3 downto 0); clk: en STD_LOGIC; in STD_LOGIC; up_enable: en STD_LOGIC); componente final updown_counter; el componente counter_clkDiv es el puerto (clk: en std_logic; sclk: fuera de std_logic); componente final counter_clkDiv; componente sseg_dec es Port (ALU_VAL: en std_logic_vector (7 downto 0); SIGN: en std_logic; VÁLIDO: en std_logic; CLK: en std_logic; DISP_EN: out std_logic_vector (3 downto 0); SEGMENTOS: out std_vector; componente final sseg_dec; el componente led_clkDiv es Puerto (present_state: en STD_LOGIC_VECTOR (3 downto 0); clk: en STD_LOGIC; led_clk: out STD_LOGIC); componente final led_clkDiv; señal present_state: STD_LOGIC_VECTOR (3 downto 0): = "0000"; señal next_state: STD_LOGIC_VECTOR (3 downto 0): = "0000"; señal estado_anterior: STD_LOGIC_VECTOR (3 downto 0): = "0000"; señal Alu_Val: STD_LOGIC_VECTOR (7 downto 0); señal sclk: STD_LOGIC; comenzar Alu_Val (7 hacia abajo 4) <= "0000"; Alu_Val (3 downto 0) <= present_state; next_state (0) <= not (present_state (0)); next_state (1) <= present_state (0) xor present_state (1); next_state (2) <= (present_state (0) y present_state (1)) xor present_state (2); next_state (3) <= (present_state (0) y present_state (1) y present_state (2)) xor present_state (3); estado_anterior (0) <= no (estado_anterior (0)); estado_anterior (1) <= estado_presente (0) xnor estado_presente (1); estado_anterior (2) <= (estado_presente (0) ni estado_anterior (1)) xor estado_presente (2); previous_state (3) sclk, next_state => next_state, previous_state => previous_state, up_enable => up_enable, down_enable => down_enable, present_state => present_state); mostrar: mapa de puertos sseg_dec (ALU_VAL => Alu_Val, SIGN => '0', VALID => '1', CLK => clk, DISP_EN => DISP_EN, SEGMENTS => SEGMENTS); led_div: mapa de puertos led_clkDiv (clk => clk, present_state => present_state, led_clk => led_clk); clk_div: mapa de puertos counter_clkDiv (clk => clk, sclk => sclk); end Behavioral;

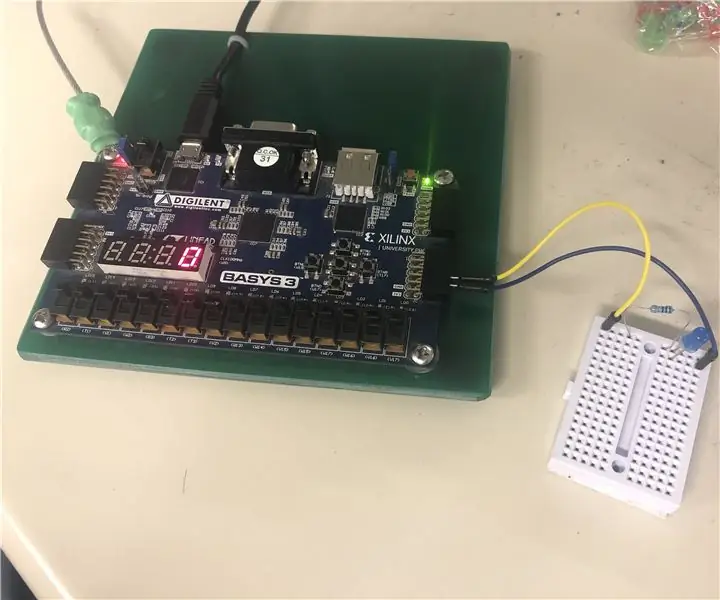

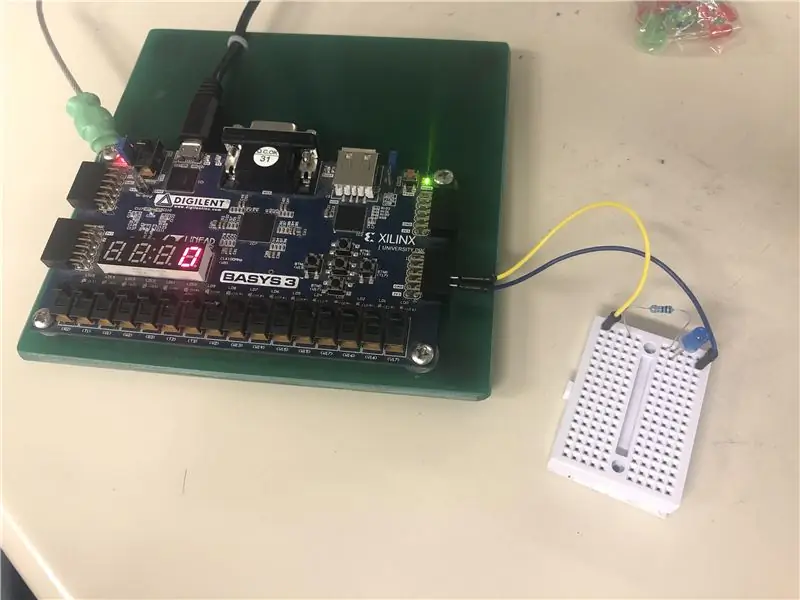

Paso 4: establecimiento de restricciones y ensamblaje

Restricciones

Para configurar y programar correctamente la placa Basys 3, primero debemos configurar nuestro archivo de restricciones que se adjunta a este paso. Se han ajustado las siguientes configuraciones:

Botones

- Se cambió T18 a "up_enable" (aumentar el brillo)

- Se cambió U17 a "down_enable" (disminuir el brillo)

Pantalla de 7 segmentos

- W7, W6, U8, V8, U5, V5, U7, V7 representan cada segmento de una pantalla

- U2, U4, V4, W4 representan cada ánodo mostrado (solo 2 están activos porque nuestro número más alto es 15)

PMOD Encabezado JC

JC7 es donde conectamos uno de los cables de la bombilla LED y el otro cable conduce a TIERRA

Después de configurar todo esto, todo lo que tiene que hacer es generar su flujo de bits (con cualquier software que esté usando, es decir, Vivado), programar su placa y ¡boom! Tienes una tabla de trabajo.

Nota: El mapeo de pines se puede encontrar en la hoja de datos de Basys 3 aquí.

Montaje

Paso 5: uso de su atenuador

Si todo va bien, debería tener un sistema de atenuación en pleno funcionamiento. Para resumir, presionar el botón superior aumentará su brillo (hasta el 15) y presionar el botón hacia abajo disminuirá su brillo (hasta 0). ¡Espero que todo vaya bien para tu vista ahora relajada!

Recomendado:

Montaje regulable del sensor ultrasónico: 9 pasos (con imágenes)

Montaje regulable del sensor ultrasónico: ¡Hola! Soy Alejandro. Estoy en octavo grado y soy estudiante del instituto tecnológico IITA.Para esta competencia he realizado un soporte regulable para un sensor ultrasónico para robótica que se puede acoplar al robot directamente oa un servo, y yo

Caja de luz LED regulable: 11 pasos

Caja de luz LED regulable: construya su caja de luz LED de 18 W para combatir la tristeza invernal. Esta caja de luz es difusa y regulable mediante PWM. Si tiene un temporizador de lámpara, puede usarlo como alternativa a un despertador

Panel LED regulable: 15 pasos (con imágenes)

Panel LED regulable: Cuando vi el concurso de LED, me puse a pensar si había algo que sería divertido de hacer con los LED usados. Realmente no soy un tipo eléctrico, así que pensé que sería un desafío divertido. Había estado buscando una lámpara de trabajo durante algún tiempo, así que

Luz de inundación LED regulable DIY: 5 pasos (con imágenes)

Luz de inundación LED regulable de bricolaje: las luces de inundación a veces tienden a dejar de funcionar con el tiempo, aunque hoy en día usan LED. Esto podría deberse a muchas razones, como un sobrecalentamiento o una falla en el controlador de LED o una falla en el proceso de fabricación. La mayoría de nosotros termina tirando una picana

¡Haga su propia iluminación de taller LED regulable !: 11 pasos (con imágenes)

¡Haga su propia iluminación LED regulable para el taller !: ¡En este Instructable, le mostraré cómo hacer su propia iluminación LED extremadamente eficiente para su taller! Nosotros, los fabricantes, nunca tenemos suficiente iluminación en nuestra mesa de trabajo, así que necesitamos comprar lámparas. Pero como creadores, no compramos cosas (y nos estafan …)