Tabla de contenido:

- Paso 1: agregue fuentes y elija "Agregar o crear fuentes de simulación

- Paso 2: crear un archivo llamado Enable_sr_tb

- Paso 3: crear un archivo de banco de pruebas

- Paso 4: establezca Enable_sr_tb como el nivel superior en la simulación

- Paso 5: Ejecute la síntesis y la simulación de comportamiento

- Paso 6: evaluar el resultado de la simulación

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:43.

- Última modificación 2025-01-23 14:40.

Hice este proyecto de simulación para una clase en línea. El proyecto está escrito por Verilog. Usaremos la simulación en Vivado para visualizar la forma de onda en enable_sr (enable digit) del proyecto de cronómetro creado previamente. Además, usaremos la tarea del sistema para mostrar el error cometido por nosotros en el diseño.

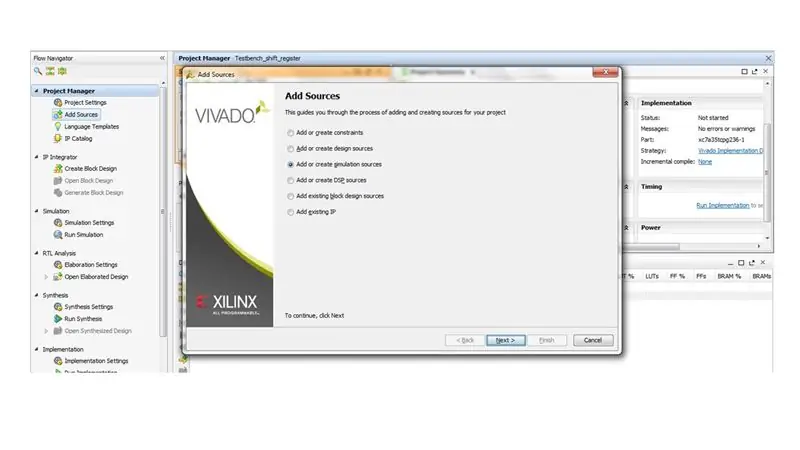

Paso 1: agregue fuentes y elija "Agregar o crear fuentes de simulación

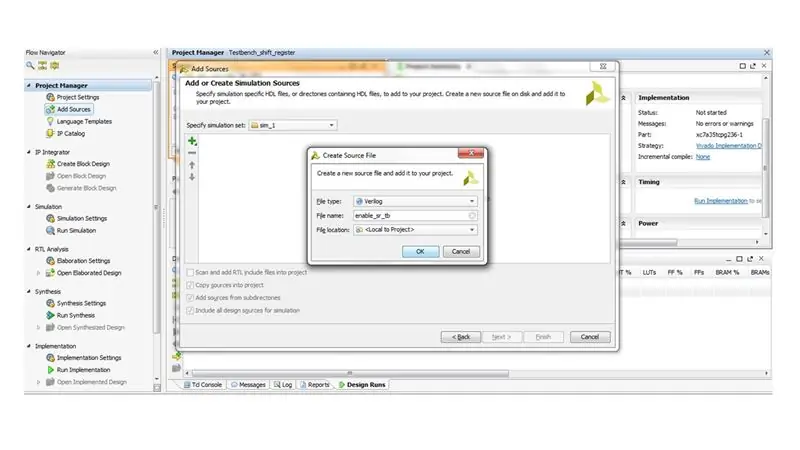

Paso 2: crear un archivo llamado Enable_sr_tb

Paso 3: crear un archivo de banco de pruebas

1. Importe el módulo enable_sr del proyecto de cronómetro. Ese es el archivo que queremos simular.

2. Cree el módulo de banco de pruebas enable_sr_tb ();

3. Introduzca las entradas y salidas del módulo enable_sr (). Recuerde que las entradas para enable_sr ahora están en el tipo de registro, mientras que las salidas se convierten en el tipo de red.

4. Cree una instancia de la unidad bajo prueba (uut) que es enable_sr

5. Genere un reloj cuyo período (T) sea 20ns

6. Utilice la declaración condicional para crear un sistema de verificación de errores. En este ejemplo, queremos comprobar si hay más de un dígito activo.

Nota: En el archivo enable_sr () original, debemos inicializar el patrón como 4’b0011 para que haya dos dígitos activos para crear un error

7. Use la tarea del sistema $ display para mostrar el error.

8. Utilice la tarea del sistema $ finish para completar la simulación en el tiempo 400ns

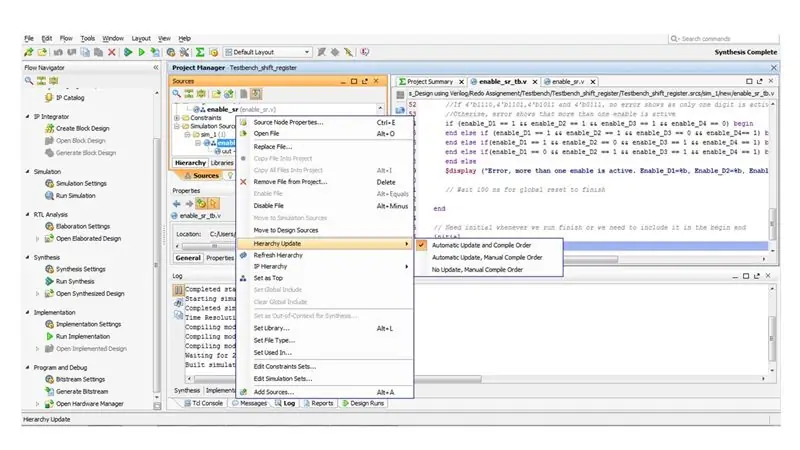

Paso 4: establezca Enable_sr_tb como el nivel superior en la simulación

Paso 5: Ejecute la síntesis y la simulación de comportamiento

- Antes de ejecutar la simulación de comportamiento, ejecute la síntesis para asegurarse de que no haya errores de sintaxis en el archivo del banco de pruebas y la unidad bajo prueba.

- Ejecute la simulación de comportamiento

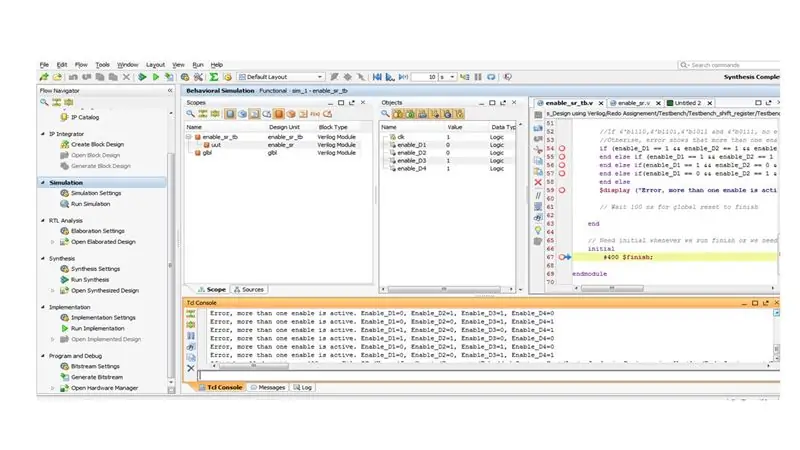

Paso 6: evaluar el resultado de la simulación

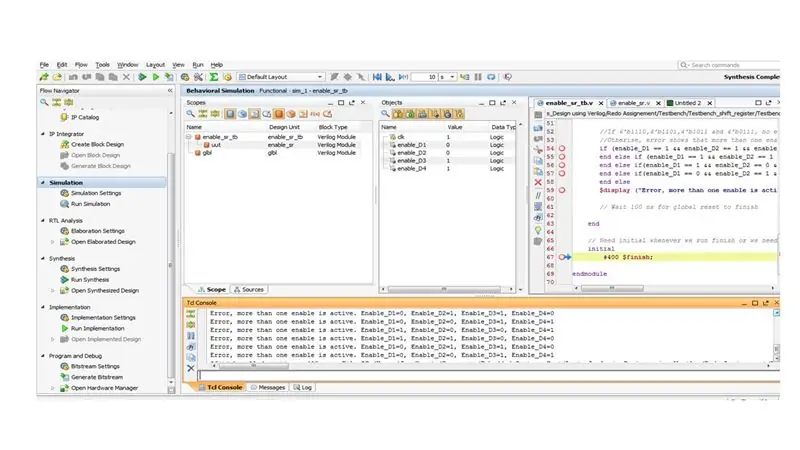

Verá las ventanas de simulación. Contiene diferentes paneles.

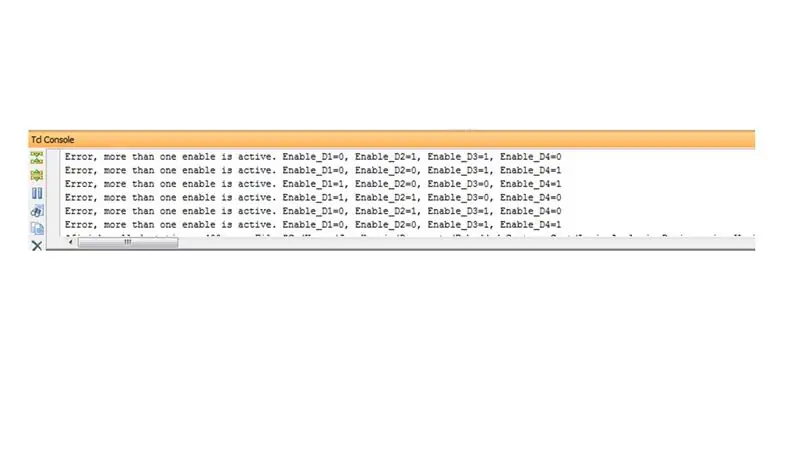

Verá el mensaje de error en el panel de la consola. Esto muestra que hay más de un dígito activo durante el período de simulación.

También puede ver la forma de onda en el osciloscopio.

Se adjunta el archivo del proyecto.

Recomendado:

Visuino Cómo utilizar el sensor de proximidad inductivo: 7 pasos

Visuino Cómo usar el sensor de proximidad inductivo: en este tutorial usaremos un sensor de proximidad inductivo y un LED conectado a Arduino UNO y Visuino para detectar la proximidad del metal

Cómo utilizar el módulo RFID-RC522 con Arduino: 5 pasos

Cómo usar el módulo RFID-RC522 con Arduino: En este Instructable, daré un tutorial sobre el principio de funcionamiento fundamental del módulo RFID junto con sus etiquetas y chips. También proporcionaré un breve ejemplo de un proyecto que hice usando este módulo RFID con un LED RGB. Como de costumbre con mis Ins

Cómo utilizar el convertidor reductor de CC a CC LM2596: 8 pasos

Cómo utilizar el convertidor reductor de CC a CC LM2596: este tutorial mostrará cómo utilizar el convertidor reductor LM2596 para encender dispositivos que requieren diferentes voltajes. Mostraremos cuáles son los mejores tipos de baterías para usar con el convertidor y cómo obtener más de una salida del convertidor (indi

Cómo utilizar un módulo de reloj en tiempo real (DS3231): 5 pasos

Cómo utilizar un módulo de reloj en tiempo real (DS3231): El DS3231 es un reloj en tiempo real (RTC) I2C extremadamente preciso y de bajo costo con un oscilador de cristal integrado con compensación de temperatura (TCXO) y un cristal. El dispositivo incorpora una entrada de batería y mantiene una indicación de la hora precisa cuando la alimentación principal a

Cómo utilizar el lector de tarjetas de memoria interno PS3 como dispositivo USB en su PC: 6 pasos

Cómo utilizar el lector de tarjetas de memoria interno de PS3 como dispositivo USB en tu PC: En primer lugar, este es mi primer Instructable (¡yippie!), Estoy seguro de que habrá mucho por venir, así que tenía una PS3 rota y quería hacer algún uso de los componentes de trabajo. Lo primero que hice fue extraer la hoja de datos del chip convertidor en la tarjeta PS3 r