Tabla de contenido:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:40.

- Última modificación 2025-01-23 14:39.

En este tutorial, usaremos la FPGA para controlar el circuito LED externo. Vamos a implementar las siguientes tareas

(A) Utilice los botones pulsadores del FPGA Cyclone IV DuePrologic para controlar el LED.

(B) Flash LED encendido y apagado periódicamente

Video de demostración

Menú de laboratorio:

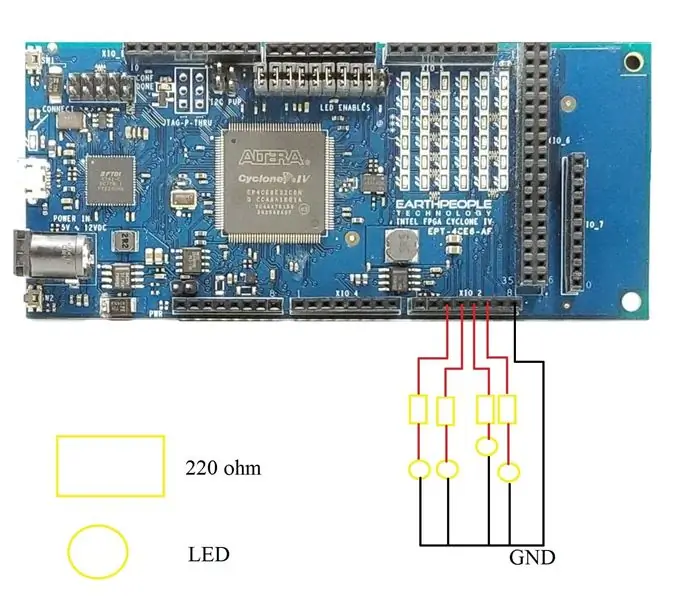

Paso 1: Construya el circuito electrónico

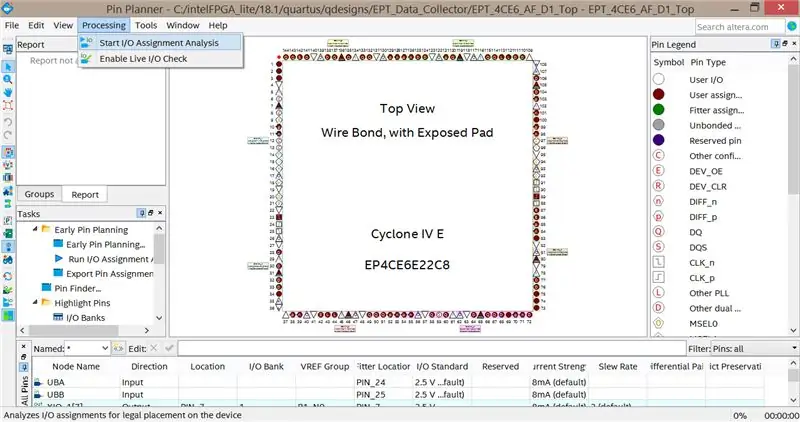

Paso 2: verifique el planificador de pines y edite el código de Verilog

Paso 3: Edite el código de Verilog

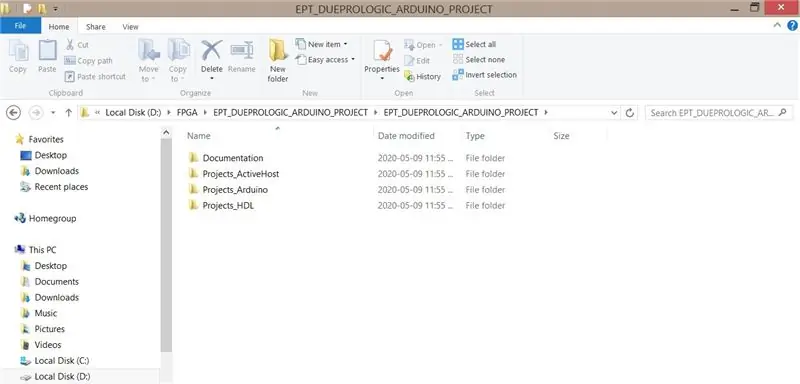

Cuando compre FPGA DueProLogic, debería recibir un DVD. Después de abrir "Projects_HDL", debería ver el archivo de código original

Agrega el código resaltado. Registra los puertos de E / S y asigna números a los puertos.

cable de salida [7: 0] XIO_1, // XIO - D2-D9

cable de salida [5: 0] XIO_2, // XIO - D10-D12

cable de salida [5: 0] XIO_3, // XIO - D22-D29

cable de entrada [5: 0] XIO_4, // XIO - D30-D37

cable de entrada [5: 0] XIO_5, // XIO - D38-D45

cable de salida [4: 0] XIO_6_OUT, // XIO - D46-D53

cable de entrada [31: 5] XIO_6, // XIO - D46-D53

cable de salida [2: 0] XIO_7, // XIO - D69, D70, D71, D74, D75, D76

cable de entrada UBA, // Interruptores de botón pulsador

cable de entrada UBB // Interruptores de botón pulsador

asignar XIO_1 [3] = start_stop_cntrl;

asignar XIO_2 [1] = start_blinky; // LED flash LED encendido y apagado

asignar XIO_2 [2] = 1'b1; // salida ALTA

asignar XIO_2 [3] = ~ UBA; // Pulsar el botón A

asignar XIO_2 [4] = UBB; // Pulsador B

asignar c_enable = XIO_5 [2];

asignar LEDExt = XIO_5 [5];

Entonces tenemos que configurar un temporizador de retardo. Comente el código del temporizador original y escriba una nueva función de temporizador

//-----------------------------------------------

// LED de inicio parpadeante

//-----------------------------------------------

/*

siempre @ (posedge CLK_66 o negedge RST)

empezar

si (! RST)

start_blinky <= 1'b0;

demás

empezar

si (control_register [7: 4]> 0)

start_blinky <= 1'b1;

demás

start_blinky <= 1'b0;

fin

fin

*/

reg [31: 0] ex;

comienzo inicial

ex <= 32'b0;

start_blinky <= 1'b0;

fin

siempre @ (posedge CLK_66)

empezar

ex <= ex + 1'b1;

if (ex> 100000000) // flash encendido / apagado ~ 1,6 segundos, reloj 66MHz

empezar

start_blinky <=! start_blinky;

ex <= 32'b0;

fin

fin

//-----------------------------------------------

// Contador de temporizador de retardo LED

//-----------------------------------------------

/*

siempre @ (posedge CLK_66 o negedge RST)

empezar

si (! RST)

led_delay_counter <= TIMER_LOW_LIMIT;

demás

empezar

si (indica [SELECT_MODE])

led_delay_counter <= valor_temporizador;

si no (indica [WAIT_FOR_TIMER])

led_delay_counter <= led_delay_counter - 1'd1;

fin

fin*/

Paso 4: compile el código Verilog

Presione "Iniciar compilación" en Quartus, no se debe generar ningún mensaje de error.

Si recibe un mensaje de error sobre varios pines. Vaya a Asignaciones -> Dispositivo -> Opciones de dispositivo y pin -> Pines de doble propósito -> cambie el valor del pin apropiado a "Usar como E / S normal".

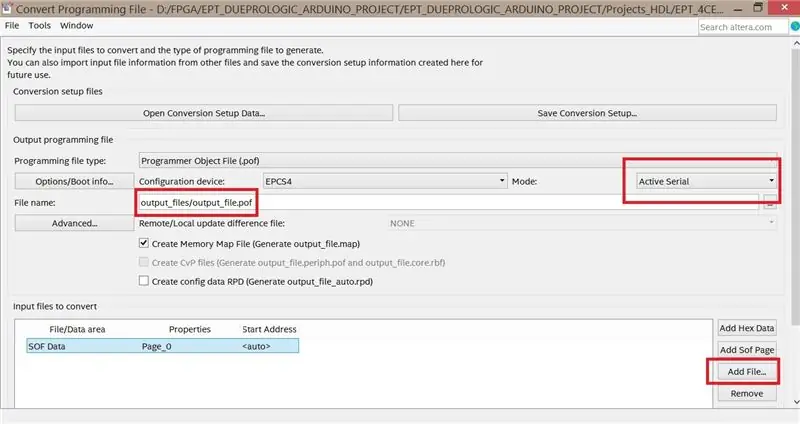

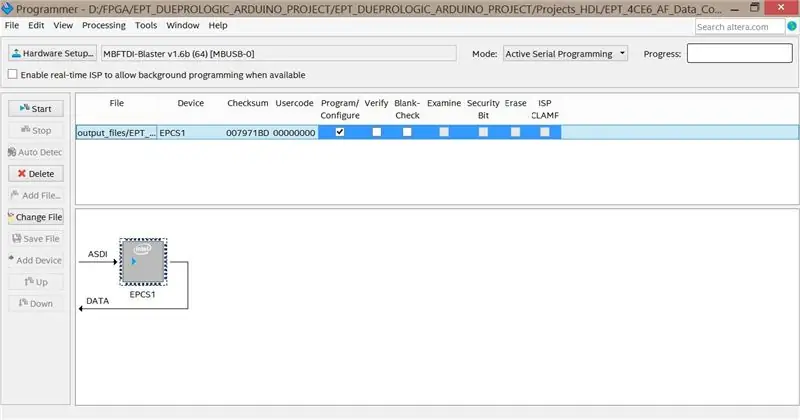

Después de la compilación, debe obtener el archivo de salida pof directamente. Si su software no está actualizado, es posible que solo obtenga el archivo sof. Cuando suceda, haga clic en "Archivo" en Quartus -> "convertir archivos de programación". Cambie la configuración que está marcada con cuadros rojos.

Paso 5: Probémoslo

Después de todo, ¡debería funcionar! El LED amarillo está siempre encendido. El LED rojo parpadea. El LED azul se apaga si presiona el botón B. El LED verde se enciende si presiona el botón A

Recomendado:

FPGA Cyclone IV DueProLogic controla la cámara Raspberry Pi: 5 pasos

FPGA Cyclone IV DueProLogic controla la cámara Raspberry Pi: a pesar de que la FPGA DueProLogic está diseñada oficialmente para Arduino, vamos a hacer comunicables la FPGA y la Raspberry Pi 4B. En este tutorial se implementan tres tareas: (A) Presione simultáneamente los dos botones en FPGA para cambiar el ángulo de

FPGA Cyclone IV DueProLogic controla el servomotor: 4 pasos

FPGA Cyclone IV DueProLogic Controls Servo Motor: En este tutorial, vamos a escribir código Verilog para controlar el servomotor. El servo SG-90 es fabricado por Waveshare. Cuando compra el servomotor, puede recibir una hoja de datos que enumera el voltaje de funcionamiento, el par máximo y el Pu propuesto

Juego Arduino Cyclone: 5 pasos (con imágenes)

Arduino Cyclone Game: Nunca he jugado el verdadero juego de arcade de cyclone pero me gusta la idea de jugar con nuestro tiempo de reacción. Diseñé un juego miniaturizado. Consta de 32 leds formando un círculo, los leds se iluminan uno a uno como un led chaser. El objetivo es presionar un botón

Cyclone (Arduino LED Game): 6 pasos (con imágenes)

Cyclone (Arduino LED Game): ¡En este tutorial, te enseñaré cómo crear un juego LED con muy poco código o experiencia! Tuve esta idea por un tiempo y finalmente comencé a crearla. Es un juego divertido que nos recuerda a todos los juegos de arcade. Hay otros tutoriales t

Cyclone LED Arcade Game: 4 pasos

Cyclone LED Arcade Game: La intención de este proyecto era crear un juego simple usando un Arduino que fuera interactivo y entretenido para los niños. Recuerdo que el juego de arcade Cyclone era uno de mis juegos de arcade favoritos cuando era más joven, así que decidí replicarlo. T