Tabla de contenido:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:41.

- Última modificación 2025-01-23 14:39.

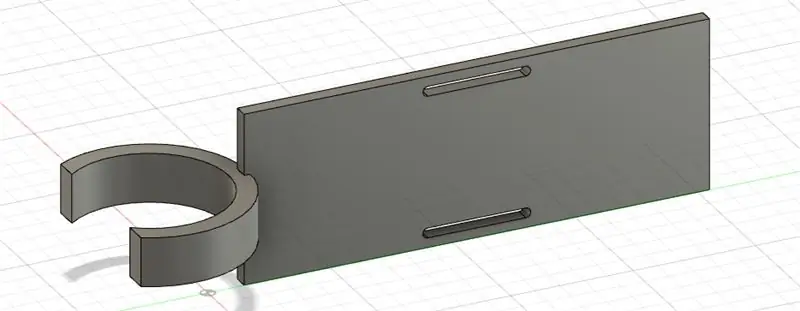

Conecte su placa de desarrollo Mojo a entradas externas con este escudo.

¿Qué es la placa de desarrollo Mojo?

La placa de desarrollo Mojo es una placa de desarrollo basada en Xilinx spartan 3 FPGA. El tablero está hecho por Alchitry. Los FPGA son muy útiles cuando se deben ejecutar múltiples procesos simultáneamente.

¿Qué vas a necesitar?

Suministros

Placa de desarrollo Mojo

Archivo Gerber

8 resistencias de 15 k ohmios (opcional *)

4 resistencias de 470 ohmios

4 resistencias de 560 ohmios

4 pantallas CC de siete segmentos

LED de 4 x 3 mm

4 x interruptores táctiles SPDT

Interruptor DIP de montaje en superficie de 1 x 4 posiciones

2 x 25 por 2 o 4 x 25 encabezados

1x cabeza de caja de 2 x 5 pines

Soldador

Soldar

Flujo

* (si se omiten estas resistencias, el pullup / pulldown interno debe estar habilitado para los pines relevantes)

Paso 1: Cargue Gerber al fabricante de PCB de su elección

Para mis placas pedí a JLC PCB.

El único cambio que hice fue el color que quería combinar con el negro del Mojo.

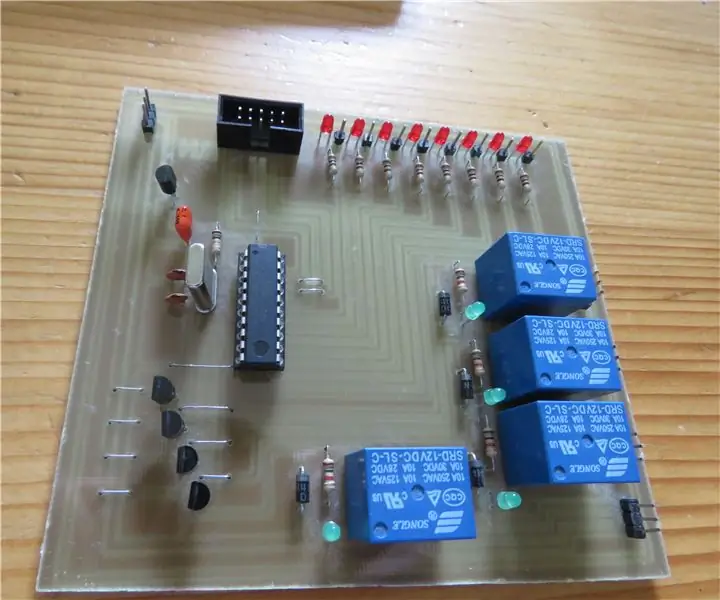

Paso 2: Montaje de la placa

Al soldar, siempre me resulta útil soldar primero las partes más bajas, por lo que comenzar con las resistencias es una buena idea.

R5, R6, R7, R8, R9, R10, R11 y R12 son resistencias de 15k ohmios que se utilizan para bajar los interruptores (si está utilizando pullup / pulldown interno, ignore esto).

R1, R2, R3, R4 son resistencias de 560 ohmios que se encargan de limitar la corriente a través de la pantalla de 7 segmentos.

R13, R14, R15, R16 son resistencias de 470 ohmios que se encargan de limitar la corriente a través de los 4 LED.

A continuación, suelde el interruptor DIP, los interruptores táctiles, los LED, las pantallas de siete segmentos y el conector del cabezal de la caja en ese orden.

Ahora coloque el 25 por 2 (o 2 25 por 1) en el mojo para alinear los pines. Alinee el escudo con los pines y suéldelo en su lugar.

Paso 3: configuración del software

Para el software, consultar el sitio web de Alchitry le permitirá saber lo que necesita para comenzar e instalar Xilinx ISE. Sin embargo, cambiar el archivo.ucf para que sepa qué pines están conectados a lo que es importante para que su programa se ejecute.

Aquí está el archivo.ucf que uso con el escudo:

CONFIG VCCAUX = 3.3;

NET "clk" TNM_NET = clk; TIMESPEC TS_clk = PERIODO "clk" 50 MHz ALTO 50%; NET "clk" LOC = P56 | IOSTANDARD = LVTTL; NET "rst_n" LOC = P38 | IOSTANDARD = LVTTL; NET "cclk" LOC = P70 | IOSTANDARD = LVTTL; NET "spi_mosi" LOC = P44 | IOSTANDARD = LVTTL; NET "spi_miso" LOC = P45 | IOSTANDARD = LVTTL; NET "spi_ss" LOC = P48 | IOSTANDARD = LVTTL; NET "spi_sck" LOC = P43 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P46 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P61 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P62 | IOSTANDARD = LVTTL; NET "spi_channel" LOC = P65 | IOSTANDARD = LVTTL; NET "avr_tx" LOC = P55 | IOSTANDARD = LVTTL; NET "avr_rx" LOC = P59 | IOSTANDARD = LVTTL; NET "avr_rx_busy" LOC = P39 | IOSTANDARD = LVTTL; NET "Q [0]" LOC = P26 | IOSTANDARD = LVTTL; NET "Q [1]" LOC = P23 | IOSTANDARD = LVTTL; NET "Q [2]" LOC = P21 | IOSTANDARD = LVTTL; NET "Q [3]" LOC = P16 | IOSTANDARD = LVTTL; NET "S [0]" LOC = P7 | IOSTANDARD = LVTTL; NET "S [1]" LOC = P9 | IOSTANDARD = LVTTL; NET "S [2]" LOC = P11 | IOSTANDARD = LVTTL; NET "S [3]" LOC = P14 | IOSTANDARD = LVTTL; NET "pb [1]" LOC = P30 | IOSTANDARD = LVTTL; NET "pb [2]" LOC = P27 | IOSTANDARD = LVTTL; NET "pb [3]" LOC = P24 | IOSTANDARD = LVTTL; NET "pb [4]" LOC = P22 | IOSTANDARD = LVTTL; NET "sevsega [0]" LOC = P57 | IOSTANDARD = LVTTL; NET "sevsegb [0]" LOC = P58 | IOSTANDARD = LVTTL; NET "sevsegc [0]" LOC = P66 | IOSTANDARD = LVTTL; NET "sevsegd [0]" LOC = P67 | IOSTANDARD = LVTTL; NET "sevsege [0]" LOC = P74 | IOSTANDARD = LVTTL; NET "sevsegf [0]" LOC = P75 | IOSTANDARD = LVTTL; NET "sevsegg [0]" LOC = P78 | IOSTANDARD = LVTTL; NET "sevsegdp [0]" LOC = P80 | IOSTANDARD = LVTTL; NET "sevsega [1]" LOC = P82 | IOSTANDARD = LVTTL; NET "sevsegb [1]" LOC = P83 | IOSTANDARD = LVTTL; NET "sevsegc [1]" LOC = P84 | IOSTANDARD = LVTTL; NET "sevsegd [1]" LOC = P85 | IOSTANDARD = LVTTL; NET "sevsege [1]" LOC = P87 | IOSTANDARD = LVTTL; NET "sevsegf [1]" LOC = P88 | IOSTANDARD = LVTTL; NET "sevsegg [1]" LOC = P92 | IOSTANDARD = LVTTL; NET "sevsegdp [1]" LOC = P94 | IOSTANDARD = LVTTL; NET "sevsega [2]" LOC = P97 | IOSTANDARD = LVTTL; NET "sevsegb [2]" LOC = P98 | IOSTANDARD = LVTTL; NET "sevsegc [2]" LOC = P99 | IOSTANDARD = LVTTL; NET "sevsegd [2]" LOC = P100 | IOSTANDARD = LVTTL; NET "sevsege [2]" LOC = P101 | IOSTANDARD = LVTTL; NET "sevsegf [2]" LOC = P102 | IOSTANDARD = LVTTL; NET "sevsegg [2]" LOC = P104 | IOSTANDARD = LVTTL; NET "sevsegdp [2]" LOC = P111 | IOSTANDARD = LVTTL; NET "sevsega [3]" LOC = P114 | IOSTANDARD = LVTTL; NET "sevsegb [3]" LOC = P115 | IOSTANDARD = LVTTL; NET "sevsegc [3]" LOC = P116 | IOSTANDARD = LVTTL; NET "sevsegd [3]" LOC = P117 | IOSTANDARD = LVTTL; NET "sevsege [3]" LOC = P118 | IOSTANDARD = LVTTL; NET "sevsegf [3]" LOC = P119 | IOSTANDARD = LVTTL; NET "sevsegg [3]" LOC = P1120 | IOSTANDARD = LVTTL; NET "sevsegdp [3]" LOC = P121 | IOSTANDARD = LVTTL;

Recuerde que si no ha instalado las resistencias desplegables para editar los pines en el.ucf con

| DERRIBAR; o

| LEVANTAR;

Si desea utilizar el bloque para algo, las conexiones son las siguientes. La izquierda es el número de pin del bloque y la derecha es el número de pin de mojo que debe asignar en su.ucf:

pin 1 = 29

pin 2 = 51

pin 3 = 32

pin 4 = 41

pin 5 = 34

pin 6 = 35

pin 7 = 40

pin 8 = 33

pin 9 = GND

pin 10 = + V

Recomendado:

Desarrollo de la placa Drivemall: 5 pasos

Desarrollo de la placa Drivemall: En este tutorial veremos los pasos básicos para crear una placa Arduino personalizada. El software utilizado es KiCad para el diseño de la placa y Arduino IDE para la creación y carga de firmware para la placa

Vocal GOBO - Escudo amortiguador de sonido - Cabina vocal - Caja vocal - Filtro de reflexión - Escudo vocal: 11 pasos

Vocal GOBO - Sound Dampener Shield - Vocal Booth - Vocal Box - Reflexion Filter - Vocalshield: comencé a grabar más voces en el estudio de mi casa y quería obtener un mejor sonido y después de algunas investigaciones descubrí lo que es un " GOBO " era. Había visto estas cosas que amortiguan el sonido, pero realmente no me di cuenta de lo que hacían. Ahora lo hago. Encontré un y

Placa de desarrollo DIY ESP32 - ESPer: 5 pasos (con imágenes)

DIY ESP32 Development Board - ESPer: Recientemente, había estado leyendo sobre muchas IoT (Internet de las cosas) y créame, no podía esperar para probar uno de estos maravillosos dispositivos, con la capacidad de conectarse a Internet, yo mismo y poner mis manos en el trabajo. Afortunadamente la oportunidad de

Haga su propia placa de desarrollo con microcontrolador: 3 pasos (con imágenes)

Haz tu propia placa de desarrollo con microcontrolador: ¿Alguna vez quisiste hacer tu propia placa de desarrollo con microcontrolador y no sabías cómo? En este instructivo te mostraré cómo hacerlo.Todo lo que necesitas es conocimiento en electrónica, diseño de circuitos y programación. Si tienes alguna misión

Jugar al juego Flappy Bird con la placa de desarrollo M5stick C basada en M5stack Esp32: 5 pasos

Jugando al juego Flappy Bird con la placa de desarrollo M5stack M5stick C basada en M5stack Esp32: Hola chicos, hoy aprenderemos cómo cargar el código del juego Flappy Bird en la placa de desarrollo m5stick c proporcionada por m5stack.Para este pequeño proyecto, necesitará lo siguiente: m5stick-c placa de desarrollo: https://www.utsource.net/itm/p/8663561.h