Tabla de contenido:

- Paso 1: diagrama de bloques

- Paso 2: Principio de funcionamiento

- Paso 3: implementación lógica

- Paso 4: resolución de interbloqueo

- Paso 5: Configuración del dispositivo - Circuito Matrix0

- Paso 6: Configuración del dispositivo - Lógica de reloj SPI

- Paso 7: Configuración del dispositivo - Propiedades de los componentes Matrix0

- Paso 8: Configuración del dispositivo - Circuito Matrix1

- Paso 9: Configuración del dispositivo: contador binario de 3 bits

- Paso 10: Configuración del dispositivo - Lógica de comparación de 3 bits

- Paso 11: Configuración del dispositivo - Lógica de comparación digital y registro temporal

- Paso 12: Configuración del dispositivo - Propiedades de los componentes de Matrix1

- Paso 13: Resultados

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:41.

- Última modificación 2025-01-23 14:39.

Los sistemas de control y los dispositivos relacionados manejan múltiples fuentes de energía, como líneas de polarización o baterías, y deben rastrear la línea más alta (o más baja) de un conjunto dado.

Por ejemplo, la conmutación de carga en un sistema alimentado por “baterías múltiples” requiere que el sistema monitoree el voltaje mínimo o máximo entre el conjunto de baterías (máximo o mínimo en función del algoritmo de conmutación particular) y enrute dinámicamente la carga al fuente más apropiada en tiempo real. Alternativamente, es posible que el sistema deba desconectar temporalmente la batería de menor voltaje para una carga adecuada.

Otro ejemplo es el sistema de energía solar moderno, donde cada panel solar está equipado con un mecanismo de rotación basculante y con un circuito de seguimiento solar (este último proporciona la información de la posición del Sol para orientar el panel). Con la información de voltaje máximo, cada posición del panel solar se puede ajustar sobre la base de que el panel de la cuerda realmente entregue el voltaje de salida más alto, logrando así un nivel superior de optimización de energía.

Hay varias marcas diferentes de circuitos integrados comerciales (principalmente microcontroladores) que, en principio, pueden implementar un seguidor de voltaje máximo. Sin embargo, requieren programación y son menos rentables que una solución de señal mixta. Complementar un diseño de Dialog GreenPAKTM puede afectar positivamente la asequibilidad, el tamaño y la modularidad del diseño. Este diseño aprovecha el beneficio de integrar circuitos analógicos y digitales en un solo chip.

En este Instructable, se implementa el front-end analógico y la lógica digital requerida para implementar un buscador de voltaje máximo (o eventualmente mínimo) entre ocho fuentes distintas.

Para implementar el monitor de voltaje máximo / mínimo analógico de 8 canales se utiliza un SLG46620G.

A continuación, describimos los pasos necesarios para comprender cómo se ha programado la solución para crear el monitor de voltaje máximo / mínimo analógico de 8 canales. Sin embargo, si solo desea obtener el resultado de la programación, descargue el software GreenPAK para ver el archivo de diseño GreenPAK ya completado. Conecte el kit de desarrollo GreenPAK a su computadora y presione el programa para crear el monitor de voltaje máximo / mínimo analógico de 8 canales.

Paso 1: diagrama de bloques

La Figura 1 muestra el diagrama global del sistema implementado.

Una cadena de hasta 8 fuentes de voltaje variable se multiplexa e interconecta con un módulo ADC de GreenPAK conectado a un diseño interno personalizado capaz de seleccionar la fuente con el voltaje más alto con respecto a las demás. La lógica interna envía esta información para su visualización o procesamiento posterior.

El diseño se basa en el producto GreenPAK SLG46620G, ya que incorpora todos los componentes básicos analógicos y digitales necesarios para la aplicación. En esta implementación, la matriz se escanea por medio de un multiplexor analógico ADG508 impulsado directamente por el GreenPAK IC.

La información de salida es un número digital de 3 bits correspondiente al número de fuente de voltaje a voltaje máximo. Una forma directa de obtener esta información es mostrar el número mediante una pantalla de 7 segmentos. Se puede lograr fácilmente conectando la salida digital del SLG46620G a un controlador de pantalla de 7 segmentos, como la solución GreenPAK descrita en la Referencia oa un IC 74LS47 común.

El circuito presentado busca voltaje máximo. Para convertir el diseño en un buscador de voltaje mínimo, se debe agregar un circuito de preacondicionamiento simple entre el multiplexor analógico y la entrada analógica GreenPAK, restando la salida del multiplexor de un voltaje de referencia de 1 V.

Paso 2: Principio de funcionamiento

El diseño tiene como objetivo seleccionar la fuente con voltaje máximo, por lo tanto, se realiza un escaneo en toda la matriz mientras se almacena el último valor máximo y se lo compara con el siguiente valor en la entrada (que pertenece a la siguiente fuente de voltaje en el escaneo).

A continuación, nos referiremos a una secuencia de multiplexación completa a lo largo de todas las entradas como un "escaneo" o "bucle".

La comparación entre dos valores no se realiza mediante componentes ACMP (sin embargo, disponibles en el SLG46620G), sino mediante el módulo DCMP, una vez que los valores se han digitalizado respectivamente. Esta es una técnica avanzada y refinada que se aborda por primera vez en la Referencia.

La Figura 2 muestra cómo está estructurado el SLG46620G para este diseño.

La señal de entrada analógica va a la entrada ADC a través del componente PGA con una ganancia establecida de 1. También son posibles varios ajustes de ganancia para encontrar la mejor combinación con la electrónica de acondicionamiento del extremo frontal dedicada a mapear los voltajes de entrada al 0-1 V gama del módulo GreenPAK ADC.

El ADC funciona en modo de un solo extremo y convierte la señal analógica en un código digital de 8 bits, que luego se transfiere al módulo DCMP. El código digital también se alimenta al bloque SPI, configurado como un búfer ADC / FSM, donde se puede almacenar un código digital y no cambiará hasta que el siguiente pulso llegue a la entrada SPI CLK. Observe que un bloque lógico dedicado controla la entrada SPI CLK. Investigaremos esta parte más adelante, ya que esta es la lógica "central" responsable del funcionamiento correcto. Un nuevo código digital se almacena en el módulo SPI solo si pertenece al voltaje de entrada máximo real.

El componente DCMP se utiliza para comparar los datos actuales de ADC con el último ganador (que es el último máximo encontrado) que se almacena en el bloque SPI. Generará un pulso en la salida OUT + cuando los nuevos datos ADC sean mayores que los anteriores. Usamos la señal OUT + para actualizar el bloque SPI con el nuevo ganador.

Una señal de reloj global impulsa las conversiones de ADC y los tiempos generales. Una vez que se realiza una conversión, la señal de salida INT del ADC pulsa, coordinada en el tiempo con la salida de datos en paralelo del ADC. Usamos la salida INT también para incrementar un contador binario de 3 bits, implementado por DFF en Matrix1, que es útil por tres razones:

1. Las líneas de salida del contador se dirigen al multiplexor analógico externo, sirviendo así el siguiente voltaje de entrada al ADC;

2. El recuento se congela en un registro de 3 bits (implementado en Matrix1) para almacenar el ganador temporal durante un escaneo;

3. El recuento se decodifica para actualizar un segundo registro de 3 bits (implementado en Matrix0) una vez que se completa un escaneo.

Paso 3: implementación lógica

El módulo ADC proporciona secuencialmente datos convertidos de todos los voltajes de entrada, uno tras otro, de forma indefinida. Una vez que el multiplexor se direcciona 0b111 (decimal 7), el contador se desplaza a 0b000 (decimal 0) iniciando así una nueva exploración de los voltajes de entrada.

Durante la exploración, la señal de salida ADC INT se genera cuando la salida de datos en paralelo es válida. Cuando esta señal pulsa, el multiplexor analógico debe cambiar a la siguiente entrada, proporcionando al PGA el voltaje correspondiente. Por lo tanto, la salida ADC INT es la señal de sincronización directa del Contador Binario de 3 bits de la Figura 2, cuya palabra de salida paralela de 3 bits se dirige directamente al multiplexor analógico externo (“V select” en la Figura 1).

Pasemos ahora a un ejemplo en el que se supone que los voltajes de entrada tienen las siguientes relaciones:

a) V0 <V1 <V2

b) V2> V3, V4

c) V5> V2

La Figura 3 representa las principales señales involucradas en el mecanismo de decisión máxima.

Dado que los datos finalmente se sincronizan en el registro de memoria intermedia SPI sincrónicamente con pulsos INT, existe una ventana de comparación donde el contenido de la memoria intermedia SPI se compara con el siguiente resultado de conversión de ADC. Esta sincronización particular da como resultado la generación de pulsos OUT + en la salida DCMP. Podemos aprovechar estos pulsos para cargar nuevos valores en el registro de búfer SPI.

Como se desprende de la línea de datos del búfer SPI de la figura anterior, el registro SPI siempre contiene, de vez en cuando, el mayor valor entre las 8 entradas y se actualiza solo cuando el módulo DCMP detecta un valor mayor (refiriéndose al DCMP OUT + línea de salida del gráfico, los pulsos faltantes hacen que V2 permanezca bloqueado en el registro hasta que se compare con V5).

Paso 4: resolución de interbloqueo

Si la lógica implementada fuera igual a la descrita anteriormente, está claro que nos toparíamos con una situación de punto muerto: el sistema es capaz de detectar solo voltajes más altos que el correspondiente a lo que está almacenado en el registro de búfer SPI.

Esto también es válido en caso de que este voltaje disminuya y luego otra entrada, hasta ahora menor que esa, se convierta en la más alta: nunca se detectaría Esta situación se explica mejor en la Figura 4 donde solo están presentes 3 voltajes de entrada por el bien de claridad.

En el momento de la iteración 2, V3 cae y V1 es el voltaje máximo real. Pero el módulo DCMP no proporciona un pulso porque los datos almacenados en el registro de búfer SPI (correspondiente a 0,6 V) son mayores que los correspondientes a V1 (0,4 V).

El sistema entonces se comporta como un buscador máximo "absoluto" y no actualiza la salida correctamente.

Una buena forma de superar este problema es forzar la recarga de los datos en el registro de búfer SPI cuando el sistema completa un ciclo de sondeo completo de todos los canales.

De hecho, si el voltaje en esa entrada sigue siendo el más alto, nada cambia y el control continúa de manera segura (refiriéndose a la Figura 4 anterior, este es el caso de las iteraciones de bucle 0 y 1). Por otro lado, si el voltaje en esa entrada por casualidad baja a un valor menor que otra entrada, entonces la recarga del valor le da la posibilidad al módulo DCMP de producir un pulso OUT + al compararlo con el nuevo valor máximo (este es el caso de iteraciones de bucle 2 y 3).

Es necesario un trozo de circuito lógico para superar el problema. Debe generar una señal de reloj para el componente SPI cuando el bucle alcanza la entrada máxima real, lo que obliga a volver a cargar su palabra de datos actualizada en el registro de búfer SPI. Esto se discutirá en las Secciones 7.2 y 7.6 a continuación.

Paso 5: Configuración del dispositivo - Circuito Matrix0

El SLG46620G tiene dos bloques Matrix, como se muestra en la Figura 2. Las siguientes figuras muestran las respectivas configuraciones del dispositivo.

La parte superior del circuito es el "Registro de bucle" realizado con 3 DFF (DFF0, DFF1 y DFF2). Se actualiza después de cada bucle del multiplexor de entrada para enviar a un controlador de pantalla de 7 segmentos el número binario del "ganador", que es la entrada con el voltaje más alto en el último escaneo. Tanto el reloj de los DFF como los datos provienen de la lógica implementada en Matrix1 a través, respectivamente, del puerto P12, P13, P14 y P15.

La parte inferior es el extremo frontal analógico con entrada en el Pin 8 y PGA con ganancia x1. La salida ADC INT va tanto a la lógica de reloj de SPI como a Matrix1 a través del puerto P0, donde servirá como señal de reloj para el contador implementado.

Las salidas de datos en paralelo ADC y SPI están etiquetadas respectivamente como NET11 y NET15 para conectarse al componente DCMP en Matrix1.

Paso 6: Configuración del dispositivo - Lógica de reloj SPI

Como se señaló anteriormente en la sección “Implementación lógica”, el registro de búfer SPI se actualiza cada vez que una comparación entre el valor real almacenado y los nuevos datos de conversión de ADC genera un pulso en la salida DCMP OUT +.

La integridad de la señal está asegurada si esta señal se realiza mediante AND con la salida ADC INT. Esto evita cualquier pico y activación falsa.

También hemos subrayado que para omitir situaciones de punto muerto, el búfer SPI debe actualizarse cuando el bucle alcance los datos reales del ganador.

Entonces, hay tres señales en el juego para una sincronización adecuada de SPI:

1. Salida ADC INT (LUT0-IN1)

2. Salida DCMP OUT + (LUT0-IN0 a través del puerto P10)

3. El recuento es igual a la señal Latch (LUT0-IN2 a través del puerto P11)

Los dos primeros son AND-ed y ambos OR-ed con el último en LUT0, cuya implementación se configura como en la Figura 6.

Paso 7: Configuración del dispositivo - Propiedades de los componentes Matrix0

Las Figuras 7-10 muestran las ventanas de propiedades de los componentes restantes que pertenecen a Matrix0.

Paso 8: Configuración del dispositivo - Circuito Matrix1

Paso 9: Configuración del dispositivo: contador binario de 3 bits

La parte superior del circuito contiene elementos lógicos, principalmente un contador binario de 3 bits sincronizado por la salida ADC INT, como ya se discutió. Este contador se implementa con un esquema bastante "estándar" que se muestra en la Figura 12.

Este contador se realiza en nuestro diseño mediante Flip-Flops DFF9, DFF10, DFF11 e INV1, LUT4, LUT8. La salida DFF9 es el LSB mientras que DFF11 es el MSB como se muestra en la Figura 13.

LUT4 está configurado como XOR mientras que LUT8 realiza la lógica AND-XOR de la Figura 12.

Las salidas de contador van a tres pines de salida digital para direccionar el multiplexor analógico externo.

LUT10 decodifica el código del contador cuando se completa un escaneo y alimenta un pulso a Matrix0 a través de DLY8 y el puerto P12. Esto se logra simplemente mediante la operación AND de las salidas del contador, decodificando así el número 7 dec (0b111 binario, fin de ciclo).

Paso 10: Configuración del dispositivo - Lógica de comparación de 3 bits

La Figura 15 muestra el circuito utilizado para detectar cuándo el bucle está iterando en la dirección "ganadora" actual. En este caso, como ya se discutió, un pulso digital debería forzar una recarga del resultado actual del ADC para resolver una posible situación de punto muerto.

La dirección "ganadora" se almacena en el registro temporal de Matrix1 (ver más abajo), mientras que la dirección actual es emitida por el contador binario.

Las puertas XNOR proporcionan una salida verdadera (1 lógica o "alta") cuando ambas entradas son iguales. Hacer Y-esta señal para todos los bits (LUT9) nos da un pulso cuando ambos códigos binarios son iguales. Los detalles sobre las puertas XOR como verificador de paridad se pueden encontrar en Referencia.

La señal "Counter-Equals-Latch" se pasa a Matrix0 a través del puerto P11.

Paso 11: Configuración del dispositivo - Lógica de comparación digital y registro temporal

La parte inferior de la Figura 11 (resaltada en la Figura 16) muestra el bloque DCMP, la parte de toma de decisiones de este diseño.

DFF6, 7 y 8 forman un registro de 3 bits para almacenar el número de entrada temporal "ganador" mientras se ejecuta el bucle. La entrada a los Flip-Flops son las salidas de contador binario de 3 bits, como se ve en el circuito global Matrix1 de la Figura 11, aquí omitidas por motivos de claridad.

Las salidas de este registro no pueden controlar directamente la pantalla de 7 segmentos porque el valor almacenado aquí cambia durante un escaneo y debe considerarse "válido" solo al final del escaneo en sí.

Por esta razón, las salidas de registro temporal se conectan al registro de bucle de Matrix0 a través de los puertos entre matrices P13, P14 y P15.

Es importante observar en la Figura 16 que el registro temporal es sincronizado por la salida DCMP OUT + cuando el ADC-SPI registra resultados de comparación en un nuevo máximo encontrado.

La misma señal OUT + se pasa a Matrix0, SPI CLK Logic, a través del puerto P10.

Paso 12: Configuración del dispositivo - Propiedades de los componentes de Matrix1

Las Figuras 17-19 muestran las ventanas de propiedades de los componentes que pertenecen a Matrix1.

Paso 13: Resultados

Para probar la implementación, se ha construido un prototipo de placa de evaluación, donde los 8 voltajes de entrada analógica se obtienen mediante una serie de divisores de resistencias con TrimPots (como se muestra en la Figura 20).

El multiplexor utilizado es un ADG508, pieza que puede funcionar con alimentación única (12 V).

El controlador de pantalla de 7 segmentos es un 74LS47. Decodifica una palabra de entrada paralela y controla directamente una pantalla de 7 segmentos de ánodo común.

La placa de evaluación tiene un conector en ángulo recto de 2x10 para conectarse directamente a una plataforma de desarrollo avanzado GreenPAK en su conector de expansión, como se muestra en la Figura 21.

La combinación con la plataforma de desarrollo avanzado GreenPAK hace que sea muy sencillo tomar medidas de las señales para una verificación rápida. Por ejemplo, la Figura 22 muestra un conjunto de señales (respectivamente CLOCK, salida ADC INT y salida DCMP OUT +) capturadas por un analizador lógico HP 54620A. Las formas de onda se activan por un flanco ascendente de la señal OUT + (en el osciloscopio etiquetado como "A> B"), por lo tanto, esta es una captura de forma de onda cuando se detecta un nuevo voltaje máximo entre las entradas analógicas. De hecho, se obtuvo girando uno de los TrimPots de la Placa de Evaluación para aumentar el voltaje correspondiente que se muestra en la Figura 22.

La Figura 23 muestra el esquema de la Junta de Evaluación.

Conclusión

En este Instructable, implementamos un buscador de voltaje máximo (o mínimo) de ocho canales para ser utilizado como una adición común a los sistemas de control multicanal. El enfoque presentado aprovecha las características avanzadas de los componentes de GreenPAK y muestra cómo es posible integrar en un solo chip funciones analógicas y digitales. Varios circuitos integrados comerciales se pueden reemplazar con Dialog GreenPAK para reducir el tamaño y el costo de la aplicación.

Recomendado:

Monitor de voltaje para baterías de alto voltaje: 3 pasos (con imágenes)

Monitor de voltaje para baterías de alto voltaje: En esta guía te explicaré cómo construí mi monitor de voltaje de batería para mi longboard eléctrico. Móntelo como desee y conecte solo dos cables a su batería (Gnd y Vcc). Esta guía asumió que el voltaje de su batería excede los 30 voltios, w

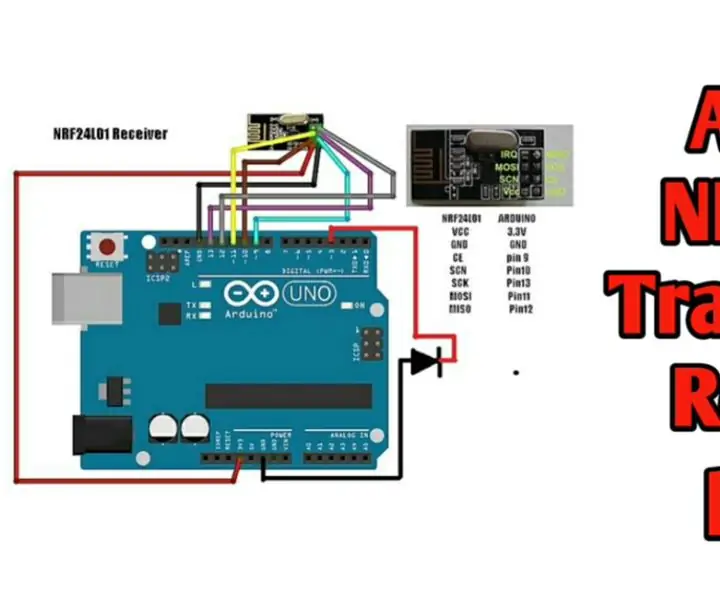

Control remoto inalámbrico con módulo NRF24L01 de 2.4Ghz con Arduino - Receptor transmisor de 4 canales / 6 canales Nrf24l01 para Quadcopter - Helicóptero Rc - Avión Rc usando Ardu

Control remoto inalámbrico con módulo NRF24L01 de 2,4 Ghz con Arduino | Receptor transmisor de 4 canales / 6 canales Nrf24l01 para Quadcopter | Helicóptero Rc | Avión Rc usando Arduino: Para operar un coche Rc | Quadcopter | Drone | Avión RC | Barco RC, siempre necesitamos un receptor y transmisor, supongamos que para RC QUADCOPTER necesitamos un transmisor y receptor de 6 canales y ese tipo de TX y RX es demasiado costoso, así que haremos uno en nuestro

Antena interior BIQUAD, fabricada en cobre y madera para recepción de canales HDTV en la banda UHF (CANALES 14-51): 7 pasos

Antena Interior BIQUAD, Fabricada en Cobre y Madera para Recepción de Canales HDTV en la Banda UHF (CANALES 14-51): En el mercado existen una variedad de antenas para televisión. Los más populares según mi criterio son: UDA-YAGIS, Dipole, Dipole con reflectores, Patch y antenas logarítmicas. Dependiendo de las condiciones, la distancia desde la transmisión a

Amplificador analógico de 8 canales para PC o HomeTheater: 12 pasos (con imágenes)

Amplificador analógico de 8 canales para PC o HomeTheater: este es mi primer instructable. Te voy a enseñar cómo hacer un amplificador de 8 canales para una computadora o sistema de audio con salidas analógicas separadas, lo he usado para mi computadora de escritorio, para ver películas, escuchar música HD y jugar juegos, además

Termómetro digital basado en Picaxe con máximo y mínimo: 13 pasos

Termómetro digital basado en Picaxe con Max y Min: (Por favor, deje un mensaje, pero no sea demasiado crítico, ¡este es mi primer instructivo!) Este es un termómetro que hice para nuestra autocaravana, para mostrar la temperatura externa. Se basa en un chip Picaxe ya que son baratos y fáciles de usar. Si esto es para