Tabla de contenido:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:40.

- Última modificación 2025-01-23 14:39.

JDM es un programador PIC popular porque utiliza un puerto serie, un mínimo de componentes y no requiere fuente de alimentación. Pero existe confusión, con muchas variaciones de programadores en la red, ¿cuáles funcionan con qué PIC? En este "instructable" ponemos a prueba JDM y demuestro cómo simular el circuito usando Spice, ¡que responderá a todas tus preguntas!

Suministros

LTspice que se puede descargar desde Analog Devices aquí.

También necesita los archivos de circuito JDM aquí.

Paso 1: Requisitos del puerto serie

JDM requiere un puerto serie que cumpla con la especificación EIA232, idealmente con niveles de voltaje + 12 / -12.

De acuerdo con la hoja de datos de Texas Instruments Line Driver MC1488 (Figura 3)

Impedancia de salida = 4 V / 8 mA = 500 ohmios.

Límite de corriente de cortocircuito = 12 mV, sin límite de tiempo, sin daño al chip.

Impedancia de entrada del receptor de línea = se recomienda de 3 k a 7 k ohmios.

Los puertos serie en las PC de escritorio más antiguas usan + 12v / -12V que cumplen con este requisito.

Los puertos serie de los equipos portátiles más nuevos utilizan voltajes más bajos. JDM puede funcionar o no; la respuesta es más compleja.

Paso 2: Requisitos de programación de PIC

La información sobre los requisitos de programación del PIC se obtiene de Microchip. Lo anterior es para un dispositivo típico.

Paso 3: Especificación JDM

¿Se ha perdido el sitio web original de JDM en la noche de los tiempos? Esto nos deja adivinando qué pretendía originalmente el diseñador para la especificación.

- Proporcione VDD = 5 V y hasta IDD = 2 mA como máximo (para la versión "en enchufe")

- Proporcione VHH = 13 V y hasta IHH = 0,2 mA como máximo.

- MCLR Tiempo de subida tVHHR = 1uS máx.

- La versión ICSP debe poder tirar de MCLR bajo contra 22k pull-up en el objetivo.

Paso 4: descripción del circuito

La figura JDM1 se basa en el circuito JDM "estándar" tomado del sitio web de PICPgm. Este es el programador “PIC in Socket” donde PIC toma energía de los pines TX y RTS. El diagrama original era difícil de entender, así que lo volví a dibujar usando la convención normal del flujo de corriente de arriba a abajo. Y agregué indicadores LED “RESET”, “PROG” y “RTS” que son necesarios durante la construcción y las pruebas. Es de esperar que estos no tengan ningún efecto perjudicial sobre el comportamiento.

La convención normal del diseño de circuitos es común a todas las conexiones a tierra, pero la característica clave de JDM es que la tierra del puerto serie (GND) está conectada a VDD. Esto crea confusión ya que las señales del puerto serie se miden con respecto a GND, las señales PIC con respecto a la tierra lógica (VSS).

Cuando TX sube, Q1 se comporta como dos diodos polarizados hacia adelante. (El colector Q1 no tiene polarización inversa como ocurre con el funcionamiento normal del transistor). El colector Q1 carga C2, que está sujeto a VDD + 8V por Zener (D3). El emisor Q1 entrega 13 V a MCLR para el modo de programación / verificación.

Cuando TX baja, el condensador C3 se carga a través de D1 y el VSS se fija en VDD-5V por zener (D5). También TX está sujeto a (VSS-0.6) por D1. Q1 está apagado, C1 mantiene su carga para el siguiente pulso de programación. MCLR está sujeto a 0 V por D2, por lo que el PIC ahora se reinicia.

Cuando RTS es alto, el reloj se transmite a PGC. D4 pinza PGC en lógica VDD alta. Cuando el RTS es bajo, el condensador C3 se carga a través de D6 y el VSS se fija en VDD-5V por zener (D5). D6 sujeta PGC en VSS o lógica 0.

Durante la programación, los datos enviados en DTR se leen en PGD, que el PIC configura como entrada. Cuando DTR es alto, Q2 actúa como "seguidor de emisor" y el voltaje de PGD es de aproximadamente (VDD-0.6) o lógica 1. Cuando DTR es bajo, Q2 actúa como un transistor defectuoso (pines de emisor y colector invertidos). Q2 baja PGD, que está bloqueado por D7 en VSS o lógica 0.

Durante la verificación, el PIC configura PGD como una salida para enviar datos al puerto serie. DTR debe establecerse alto y los datos se leen en CTS. Cuando la salida PGD es alta, Q2 está apagado, CTS = DTR = + 12V. Cuando la salida PGD es baja, Q2 está encendido. El colector Q2 consume corriente (12V + 5V) / (1k + 1k5) = 7mA de DTR y tira CTS bajo, a VSS.

Paso 5: Prepárese para la simulación

Descargue LT spice, guarde y abra los archivos de circuito (*.asc) proporcionados aquí. Para simular el circuito, debemos darle algunas entradas, luego “rastrear” las salidas. V1, V2 V3 simula el puerto serie de 12V con impedancia de salida R11, R12, R13.

- V1 genera 2 pulsos de programa en TX de 0.5ms a 4.5ms

- V2 genera ráfagas de pulsos de datos en DTR de 1,5 a 4,5 ms

- V3 genera ráfagas de pulsos de reloj en RTS de 0,5 a 3,5 ms

Los componentes V4, X1, R15 y R16 son todos parte de la simulación.

- V4 genera 2 pulsos de 2.5 a 4.5ms para verificar los datos.

- El puente X1 simula SALIDA en PGD.

- R15, R16 simulan la "carga" de PIC en VDD y MCLR.

Paso 6: Modificaciones para ICSP

La figura JDM3 muestra la versión para programación "en circuito". Las modificaciones del original son

- Reemplace el zócalo ZIF con el conector ICSP.

- El PIC ahora está alimentado por suministro al circuito de destino (V5).

- Retire el zener de 5V (D5).

- El pequeño condensador de 100pF (C4) se mueve junto al PIC en el circuito de destino.

- Los LED toman energía de la placa de circuito siempre que sea posible.

- La resistencia pull-up MCLR (R10) y el diodo (D10) son necesarios en el circuito de destino.

- ADVERTENCIA. La placa de destino debe tener un suministro "flotante", idealmente una batería.

- No conecte la tierra de destino (VSS) a la tierra de la computadora / PC conectando cualquier otro puerto de la computadora al mismo tiempo que JDM.

Después de simular JDM1, se hizo evidente el problema del tiempo de carga prolongado en C2. Luego, después de leer Fruttenboel, parece que C2 y Q1 se agregaron como una modificación al original. No puedo pensar en lo que pretenden hacer C2 y Q1 aparte de crear problemas. Entonces, para JDM4, volvemos al diseño anterior en Fruttenboel, que es simple y fácil de entender. Abrazadera D1 y D3 / LED2 MCLR entre VSS y VDD + 8V. El valor de R1 se reduce a 3k3, lo suficiente para iluminar el LED2 a 12V.

JDM4 también está diseñado para funcionar con puertos serie más débiles. Cuando TX sube (+ 9V), fuente de corriente TX = (9-8) / (1k + 3k3) = 0.2ma, lo suficiente para elevar el MCLR, aunque es insuficiente para iluminar el LED2. Cuando TX baja (aproximadamente -7V), disipador de corriente TX = (9-7) / 1k = 2mA. Corriente LED1 = (7-2 para led) / (2k7) = 1.8mA. Corriente de bajada MCLR = 7-5.5 / 3k3 = 0.5mA.

Este circuito también ha sido probado (simulación JDM5) para ver qué sucede con los puertos serie +/- 7V mínimo, donde no hay voltaje suficiente para sostener VHH = 13V. El propósito de C1 ahora se hace evidente, C1 crea un impulso corto + ve a MCLR, un pico de 33us en el borde ascendente de TX, lo suficientemente largo para que el PIC entre en modo de programación, ¿quizás? Pero retire el puente X2 (deshabilite el LED1) ya que no hay corriente suficiente para bajar el MCLR e iluminar el LED1 juntos. Cuando TX baja, disipador de corriente TX = (7V-5.5V) / (1k + 3k3) = 0.3mA, lo suficiente para bajar MCLR contra el R10 de pull-up.

Paso 7: Resultados de la simulación

Para ver los archivos gráficos, es mejor hacer clic con el botón derecho en los enlaces a continuación y seleccionar "Abrir enlace en una nueva pestaña".

Simulación 1: seguimiento de MCLR, VSS y RTS para JDM1 original. Inmediatamente las observaciones 1, 2 y 3 son evidentes.

Simulación 2: seguimiento de MCLR y VSS, y RTS para JDM2 modificado, que soluciona problemas anteriores.

Simulación 3: rastreo de PGD, VSS y PGC para JDM2 enviando datos en modo programa. Observación 4 a 3,5 mS.

Simulación 4: rastreo de PGD, VSS y CTS para JDM2 en modo de verificación (puente X1 insertado). OK

Simulación 5: traza de MCLR, VSS, PGD y PGC para JDM3. ICSP que usa energía del circuito resuelve muchos problemas.

Simulación 6: rastreo de MCLR, VSS, PGD y PGC para JDM4 con puerto serie +/- 9V. MCLR se eleva de inmediato, en pleno funcionamiento.

Simulación 7: seguimiento de MCLR, VSS y TX para JDM5 con puerto serie +/- 7V y puente X2 eliminado. C1 crea un impulso + ve (pico) en el borde ascendente de MCLR, lo suficiente para empujar MCLR por encima de TX a 13V.

Paso 8: Conclusiones

Spice es realmente bueno para revelar "secretos ocultos" del funcionamiento del circuito. Evidentemente, el circuito JDM funciona y es compatible con muchos chips PIC, pero las siguientes observaciones revelan posibles limitaciones / problemas de compatibilidad / fallas.

- Tiempo de subida prolongado de MCLR mientras C2 se carga a VPP en el primer pulso de TX. No cumple con la especificación 3.

- El puerto serie carga C2 cuando TX sube y RTS baja. Pero RTS también tiene la función de cargar C3. Cuando ambos ocurren al mismo tiempo, esto crea más carga en RTS, en consecuencia, C3 pierde carga (VSS aumenta) a 2ms en la simulación. No cumple con la especificación 1.

- C3 pierde carga (VSS comienza a subir) después de que los pulsos del reloj se detienen a 3,5 ms.

- ¿Cuál es el propósito de C2, es necesario en absoluto?

Soluciones

- Presumiblemente, PICPgm utiliza un software "alternativo". ¿Debe aplicar un pulso de TX largo para precargar a C2, luego ingresar al modo de programación solo después del segundo pulso de TX? Para la simulación, reduje el valor de C2 a 1uF para dar un tiempo de subida de 1ms. No es una solución ideal.

- Divida C2 y C3 para que se carguen de forma independiente. Una pequeña modificación a JDM2, C2 se refiere a GND en lugar de VSS.

- Resuelto por JDM3. ICSP es mucho más confiable ya que PIC es alimentado por un circuito de destino.

- JDM4 resuelve el problema 1. Este es un diseño sencillo que elimina C2 por completo.

Paso 9: Y finalmente

La prueba del pudín está en comer. Este JDM funciona, así que sigue usándolo.

Y mis recomendaciones son:

- use JDM2 para la programación de enchufes y puertos seriales de 12V,

- use JDM4 para el programador ICSP y los puertos serie por encima de +/- 9V,

- use JDM4 con el puente X2 eliminado para los puertos serie por encima de +/- 7V.

Referencias:

Especias Analog Devices LT

picpgm

Fruttenboel

Siga más proyectos de PIC en sly-corner

Recomendado:

Revisión de Elegoo Super Started Kit Uno R3: 4 pasos

Revisión del Elegoo Super Starter Kit Uno R3: Hace unos días, Elegoo me envió este Super Starter Kit para probarlo. Entonces, veamos qué hay dentro. Al abrir este estuche compacto, podemos ver muchas cosas. En la portada hay un índice con todos los componentes. En el interior tenemos una tarjeta de agradecimiento con todas las s

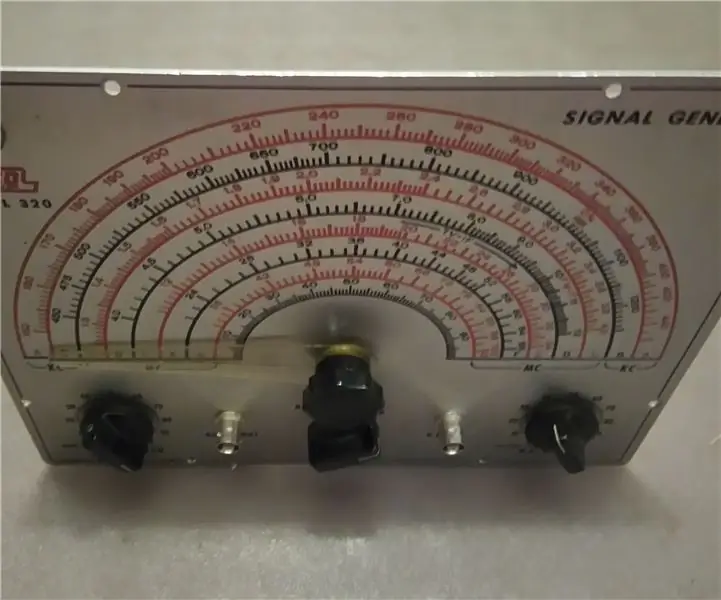

Revisión completa del generador de señales Vintage: 8 pasos

Revisión completa de Vintage Signal Generator: Adquirí un generador de señal de RF Eico 320 en una reunión de intercambio de radioaficionados por un par de dólares hace unos años, pero nunca pude hacer nada con él hasta ahora. Este generador de señales tiene cinco rangos conmutables de 150 kHz a 36 MHz y con ha

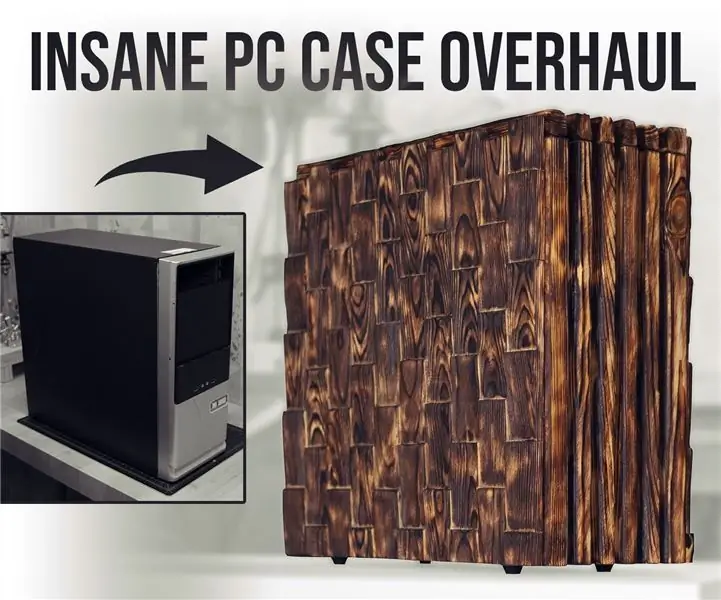

Revisión de la carcasa de PC demencial: 23 pasos (con imágenes)

Revisión de la carcasa de PC insana: En este video / instructivo, haré una modificación relativamente simple para obtener un aspecto radicalmente diferente de una PC de escritorio antigua, pero no es solo por el aspecto. El flujo de aire para los componentes internos también será mucho mejor. Y eso permitirá que p

Reparación y revisión del obturador Olympus Pen-EE: 16 pasos

Reparación y revisión del obturador Olympus Pen-EE: El Olympus Pen-EE, de aproximadamente 1961, se puede desmontar con cuidado, limpiar y reacondicionar, y volver a montar sin mucho riesgo de perder piezas o dañar algo en el interior, si tiene la mano. , firme y paciente, y tiene la herramienta adecuada

Guía de revisión de Acer Extensa Laptop 5620 Hotrod: 12 pasos

Acer Extensa Laptop 5620 Hotrod Overhaul Guide: Nuestro pequeño Acer Extensa 5620 ha sido bueno con nosotros estos últimos dos años, ¿eh? Es una máquina bastante agradable … pero … tú también lo estás sintiendo, ¿verdad? Funciona un poco lento, el disco duro hace algo de ruido, la batería dura menos de veinte minutos … es el momento