Tabla de contenido:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:44.

- Última modificación 2025-01-23 14:40.

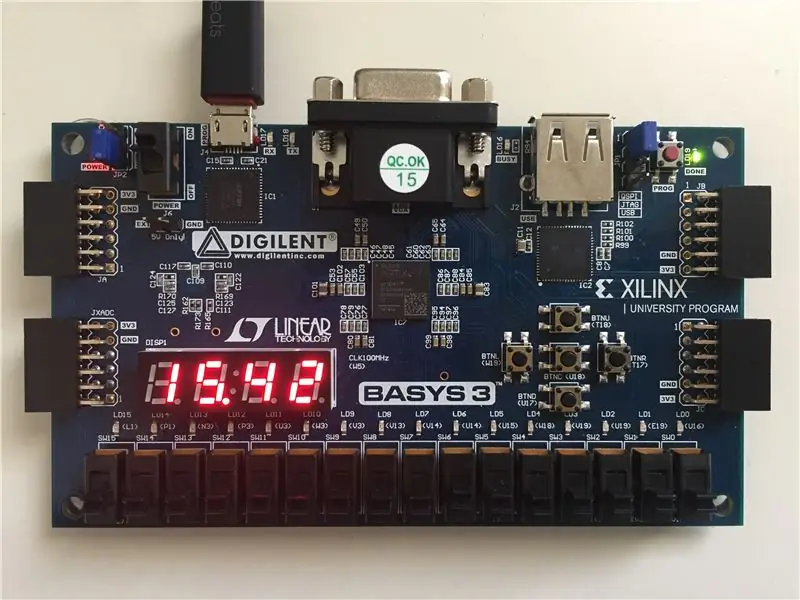

Este es un tutorial sobre cómo hacer un cronómetro usando VHDL y una placa de circuito FPGA, como una placa Basys3 Atrix-7. El cronómetro puede contar desde 00,00 segundos hasta 99,99 segundos. Utiliza dos botones, uno para el botón de inicio / parada y otro para el botón de reinicio. Los números se muestran en la pantalla de siete segmentos del tablero usando sus ánodos y cátodos. Se necesitan tres archivos diferentes para que este cronómetro funcione.

Paso 1: hardware / software

- Placa FPGA Basys3 Atrix-7

- Suite Vivado Design de Xilinx

- USB 2.0 A macho a Micro-B macho

Paso 2: diagrama de bloques

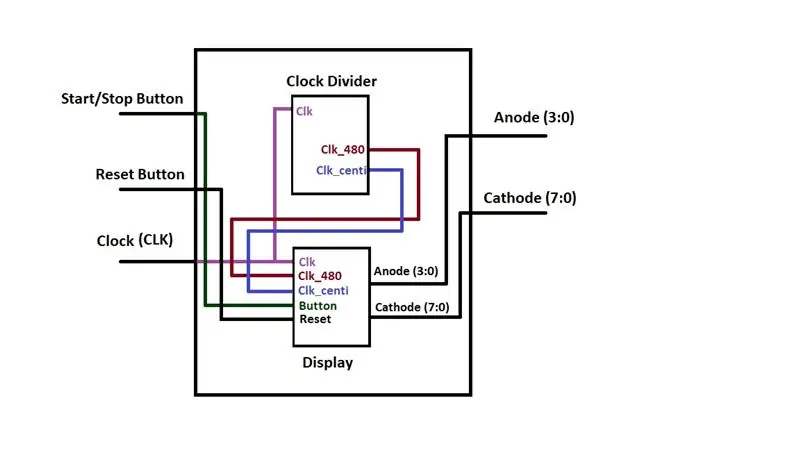

El cronómetro general tiene tres entradas y dos salidas. Las tres entradas son inicio / parada, reinicio y reloj. El inicio / parada y el reinicio son botones y el reloj es el reloj de 100MHz de la placa. Las dos salidas son los ánodos y los cátodos para la pantalla de siete segmentos.

El primer módulo (divisor de reloj) tiene una entrada y dos salidas. La entrada es el reloj de 100MHz de la placa y las salidas son dos relojes separados, uno corriendo a 480Hz y otro corriendo a 0.5MHz.

El segundo módulo (pantalla) tiene cinco entradas y dos salidas. Las entradas son el reloj de 100 MHz de la placa, los dos relojes del módulo divisor de reloj y los botones de inicio / parada y reinicio. Las salidas son los ánodos y los cátodos.

El último módulo (modelado por todo el diagrama de bloques) tiene tres entradas y dos salidas. Este es el archivo que reúne todo. Las entradas son los 100MHz de la placa y los botones de inicio / parada y reinicio. Las salidas son los ánodos y cátodos que controlan la pantalla de siete segmentos. Todas las entradas y salidas están físicamente en la placa para el módulo final.

Paso 3: diagrama de estado

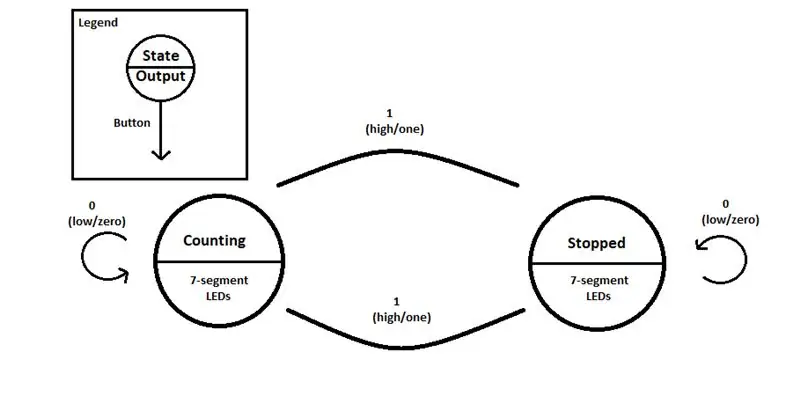

La imagen de arriba muestra el diagrama de estado de cómo funciona el cronómetro. Presionar el botón de reinicio no afecta el estado del cronómetro. El siguiente estado está determinado por el botón de inicio / parada. El inicio / parada es "ALTO" cuando se presiona, pero no cuando se mantiene presionado, y "BAJO" cuando el botón se ha recuperado o se ha mantenido presionado después de estar "ALTO" momentáneamente.

Si el cronómetro está contando y el botón de inicio / parada se pone "ALTO", entonces deja de contar. Si el cronómetro se detiene y el botón de inicio / parada se pone en "ALTO", comienza a contar de nuevo. Para ambos estados, si el botón de inicio / parada está "BAJO", permanecerá en el estado en el que se encuentra actualmente.

Paso 4: Módulo divisor de reloj

El módulo divisor de reloj tiene una entrada, el reloj de 100MHz de la placa y dos salidas, los relojes de 480Hz y 0.5MHz. El reloj de 480Hz se usa para mantener todos los LED en la pantalla de siete segmentos "encendidos" al mismo tiempo al cambiar rápidamente entre los cuatro. El reloj de 0.5MHz se usa para que el cronómetro cuente en centisegundos.

Paso 5: Módulo de visualización

Este módulo de visualización tiene cinco entradas, el reloj de 100 MHz de la placa, los dos relojes del módulo de reloj y los botones de inicio / parada y reinicio, y dos salidas, los ánodos y los cátodos. Este módulo también tiene la "lógica" de cómo cuenta el cronómetro e incorpora la máquina de estados finitos.

Paso 6: Módulo de enlace

Este último módulo es el que une a los otros dos módulos. Tiene tres entradas, el reloj de 100MHz de la placa y los botones de inicio / parada y reinicio, y dos salidas, los ánodos y los cátodos. El reloj de 100MHz va al módulo divisor de reloj y al módulo de visualización, y los botones de inicio / parada y reinicio van al módulo de visualización. Las salidas del módulo divisor de reloj (480 Hz y 0,5 MHz) van a las dos entradas de reloj del módulo de visualización. Las salidas del módulo de visualización (ánodos y cátodos) van a las salidas del módulo final.

Paso 7: restricciones

Las dos entradas pueden ser cualquier botón de la placa FPGA Basys3 Atrix-7 y las salidas serán los cuatro ánodos y los ocho cátodos (porque también desea un punto decimal entre segundos y milisegundos) para la pantalla de siete segmentos.

Paso 8: ¡Listo

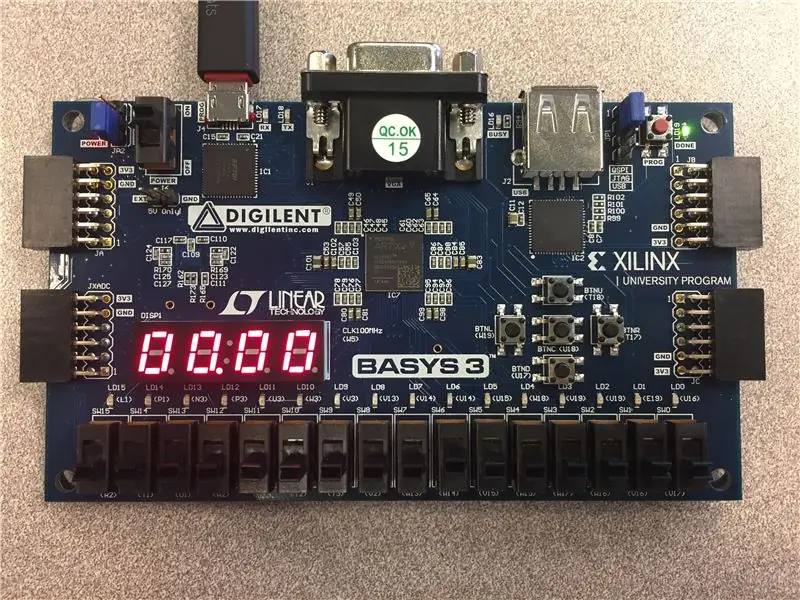

¡Cargue el programa en su placa FPGA Basys3 Atrix-7 y presione el botón de inicio / parada para poner en marcha el cronómetro!

Recomendado:

Cronómetro de Croakers: 16 pasos (con imágenes)

Cronómetro de los croakers: si sonríes a las ranas, algunas de ellas vibrarán. Al comprender el movimiento, se puede saber la hora: una operación inestable. Ranas " mirando hacia arriba " representan horas en binario (de izquierda a derecha; 8,4,2,1). Ranas " mirando hacia adelante " representar min

Cronómetro digital todo en uno (reloj, temporizador, alarma, temperatura): 10 pasos (con imágenes)

Cronómetro digital todo en uno (reloj, temporizador, alarma, temperatura): Estábamos planeando hacer un temporizador para alguna otra competencia, pero luego también implementamos un reloj (sin RTC). A medida que nos adentramos en la programación, nos interesamos en aplicar más funcionalidades al dispositivo y terminamos agregando DS3231 RTC, ya que

Cómo hacer un cronómetro usando Arduino: 8 pasos (con imágenes)

Cómo hacer un cronómetro con Arduino: este es un cronómetro con pantalla LCD Arduino 16 * 2 muy simple ……….. Si te gusta este instructable, suscríbete a mi canal https://www.youtube.com / ZenoModiff

Cronómetro básico con placa VHDL y Basys3: 9 pasos

Cronómetro básico con placa VHDL y Basys3: Bienvenido al instructivo sobre cómo construir un cronómetro usando VHDL básico y placa Basys 3. ¡Estamos emocionados de compartir nuestro proyecto contigo! Este fue un proyecto final para el curso CPE 133 (Diseño digital) en Cal Poly, SLO en el otoño de 2016. El proyecto que construimos

Cronómetro de un minuto VHDL: 5 pasos

Cronómetro de un minuto VHDL: este es un tutorial sobre cómo construir un cronómetro de un minuto usando VHDL y una placa Basys 3. Tal dispositivo es ideal para juegos en los que cada jugador tiene un máximo de un minuto para realizar su movimiento. El cronómetro muestra con precisión los segundos y milisegundos de