Tabla de contenido:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:42.

- Última modificación 2025-01-23 14:39.

Sé lo que piensas: "¿Eh? Hay muchos Instructables sobre cómo usar microcontroladores para medir la frecuencia de la señal. Bostezo". Pero espere, hay una novedad en este: describo un método para medir frecuencias mucho más altas que las que puede soportar un microcontrolador (MCU) y el ciclo de trabajo de la señal, ¡todo al mismo tiempo!

El rango de frecuencia del dispositivo se extiende desde ~ 43 Hz a ~ 450 kHz, mientras que el ciclo de trabajo varía desde el 1% hasta el 99%.

Permítanme explicar la parte "puede soportar": una MCU mide el período de una señal de onda cuadrada, T, mediante el seguimiento del tiempo entre dos eventos de transición posteriores. Por ejemplo, saltos de voltaje de bajo a alto en uno de sus pines de E / S. Lo hace contando el número de pulsos de su propio reloj interno. Ingenuamente, el límite superior de las frecuencias medidas debería obedecer al teorema de muestreo de Nyqvist-Shannon; es decir, sería aproximadamente igual a la mitad de la frecuencia de reloj de la MCU. En realidad, el límite es mucho, mucho menor, porque la MCU debe ejecutar código para manejar interrupciones, guardar variables, realizar operaciones aritméticas, mostrar resultados, etc. En mis experimentos con una MCU de 48 MHz, el número mínimo de ciclos de reloj entre transiciones medibles fue aproximadamente 106. Por lo tanto, el límite superior del rango de frecuencia medible en este caso sería 48, 000/212/2 = 226,4 kHz.

Si bien la MCU mide el período de la señal, también puede determinar su ancho de pulso, P: el tiempo que permanece alto el voltaje de la señal. En otras palabras, el tiempo entre las transiciones de menor a mayor y de mayor a menor. El ciclo de trabajo de la señal se define entonces como el siguiente porcentaje:

Deber = 100% * P / T

Al igual que en el caso de la frecuencia, existe un límite práctico en el ancho de pulso. Usando el ejemplo anterior, 106 ciclos de reloj limitarían el ancho del pulso a no menos de 2.21 microsegundos. O no menos del 50% a 226,4 kHz.

Una de las formas de aumentar el límite de frecuencia superior de las señales de onda cuadrada es la aplicación de divisores digitales que utilizan flip-flops. Dividir la frecuencia de entrada por n ampliaría el rango superior medible n veces. Esta es una gran noticia, los divisores digitales tienen un defecto fundamental: la señal dividida pierde la información de ancho de pulso (y ciclo de trabajo). Debido a la forma en que funcionan los divisores, su salida siempre tiene un ciclo de trabajo del 50%. Gorrón…

En las siguientes páginas, sin embargo, mostraré cómo dividir digitalmente la frecuencia y preservar el ancho de pulso original, lo que me permite medir señales mucho más allá de los límites impuestos por el conteo directo.

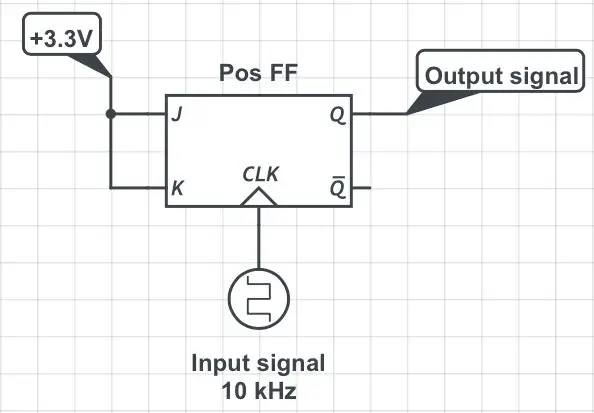

Paso 1: División de frecuencia digital

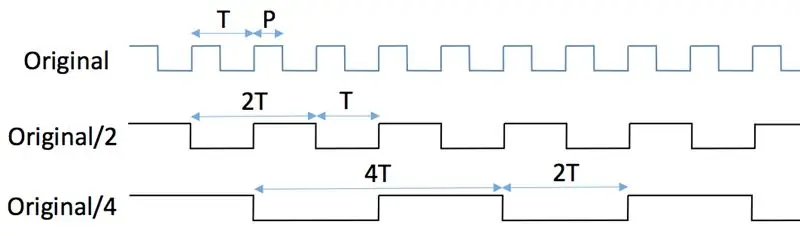

Los divisores de frecuencia digitales tradicionales utilizan flip-flops; este tutorial explica muy bien los principios de cómo construir divisores usando flip-flops JK estándar. Esto resuelve el problema de las frecuencias de entrada demasiado altas para la MCU, pero tiene un inconveniente importante: la señal dividida tiene un ciclo de trabajo del 50% independientemente del trabajo de la señal de entrada. Para ver por qué es así, mire las dos primeras cifras. La señal original con período T y ancho de pulso P se alimenta al pin de reloj de un flip-flop JK mientras sus pines J y K se mantienen altos en todo momento (primera figura). Se asume una lógica de 3.3V en todo momento. Supongamos que el flip-flop es activado por el flanco positivo (es decir, ascendente) del reloj. En estas condiciones, los cambios del estado del pin de salida ("flips" y "flops" individuales) ocurren cada vez que el pin del reloj pasa de bajo a alto. La transición de alto a bajo del reloj (es decir, el borde negativo) se ignora por completo. Vea la segunda figura. El pin de salida, Q, emite una señal cuyo período es dos veces más largo que el período original, es decir, su frecuencia se reduce a la mitad. El ancho de pulso de la salida es siempre igual a T. En consecuencia, se pierde el ancho de pulso original, P.

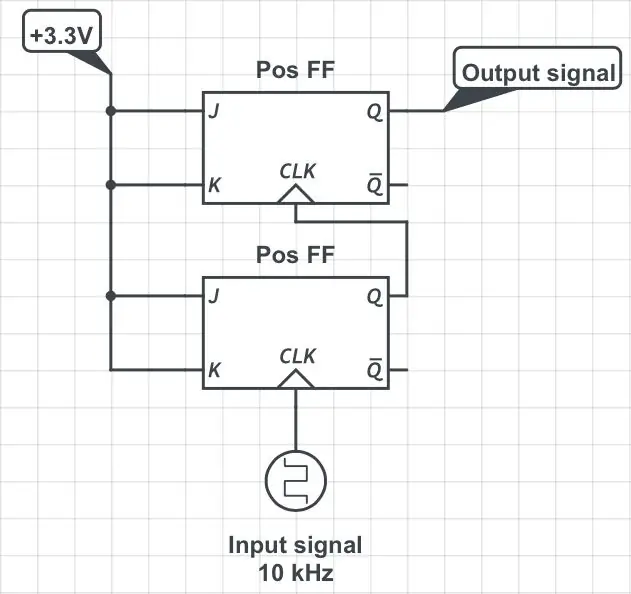

Al agregar otro flip-flop JK en una configuración que se muestra en la tercera figura, se divide la frecuencia original por 4. Al agregar más flip-flops de la misma manera secuencial, se divide la frecuencia entre las potencias subsiguientes de 2: 8, 16, 32, etc.

Problema: ¿cómo dividir la frecuencia de una onda cuadrada conservando su ancho de pulso?

La idea es agregar correctamente un flip-flop JK activado por borde negativo a la mezcla. Llamémoslo "Neg FF"; ver cuarta figura. Aquí, "correctamente" significa que los pines J y K del nuevo flip-flop están conectados a los pines de salida Q y Qbar, respectivamente, del divisor por 4 ("Pos FF") ilustrado en la figura anterior. (Aquí, "bar" es la barra horizontal sobre el símbolo Q que indica negación lógica). Para ver lo que esto logra, eche un vistazo a la tabla de funciones del "Neg FF" en la quinta figura: pines de salida de Neg, Q y Qbar, reflejan el estado de sus pines de entrada, J y K, respectivamente. Lo que significa que reflejan el estado de Pos 'Q y Qbar. Pero, la acción de flip-flop del Neg debe esperar el borde negativo de la señal original, que llega en el momento P después del borde positivo. ¡Ajá!

Las formas de onda resultantes se ilustran en la sexta figura. "Pos Q" emite la señal a 1/4 de frecuencia, "Pos Qbar" es inversa, "Neg Q" sigue a "Pos Q" desplazado por el ancho de pulso P, y "Neg Qbar" es su inverso. Puede verificar que el Y lógico de "Pos Qbar" y "Neg Q" produce un tren de pulsos caracterizado por el ancho de pulso original P y 1/4 de la frecuencia. ¡Bingo!

Al principio usé exactamente esta señal de salida para alimentar la MCU. Sin embargo, resultó ser problemático para anchos de pulso muy cortos debido a la limitación de 106 ciclos de MCU mencionada en la Introducción. He resuelto este pequeño problema eligiendo otra salida: "Pos Qbar" Y "Neg Qbar" en su lugar. Una mirada a las formas de onda debería convencerle de que el ancho de pulso de esta forma de onda en particular, P ', varía entre T y 2T en lugar del rango (0, T) para P. La P se puede recuperar fácilmente de P' mediante:

P = 2T - P '

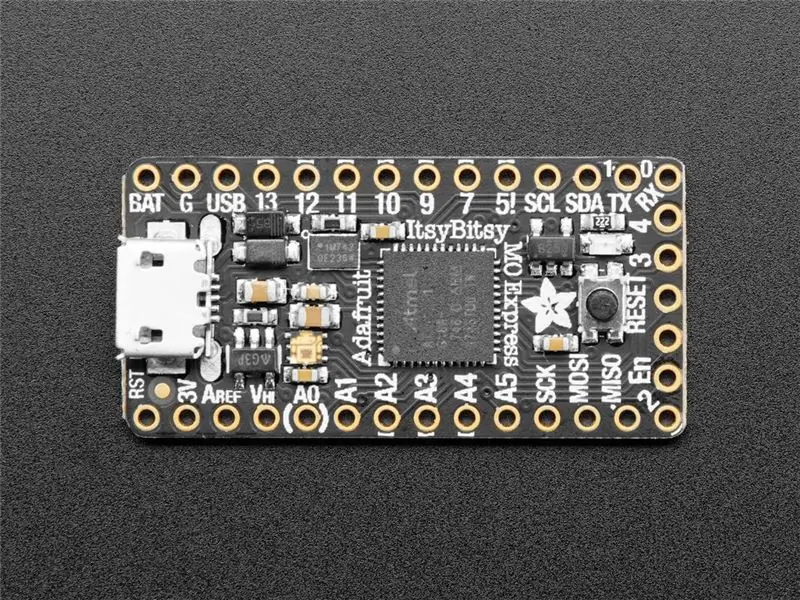

Paso 2: Hardware recomendado

Realmente me gusta el relativamente nuevo para los aficionados a la electrónica: las MCU Atmel SAM D21 basadas en el procesador ARM Cortex M0 + de 32 bits que funcionan a una frecuencia de reloj de 48 MHz, mucho más alta que las Atmel más antiguas. Para este proyecto compré:

- Placa MCU ItsyBitsy M0 Express de Adafruit

- Tenía una batería LiPo recargable de Adafruit

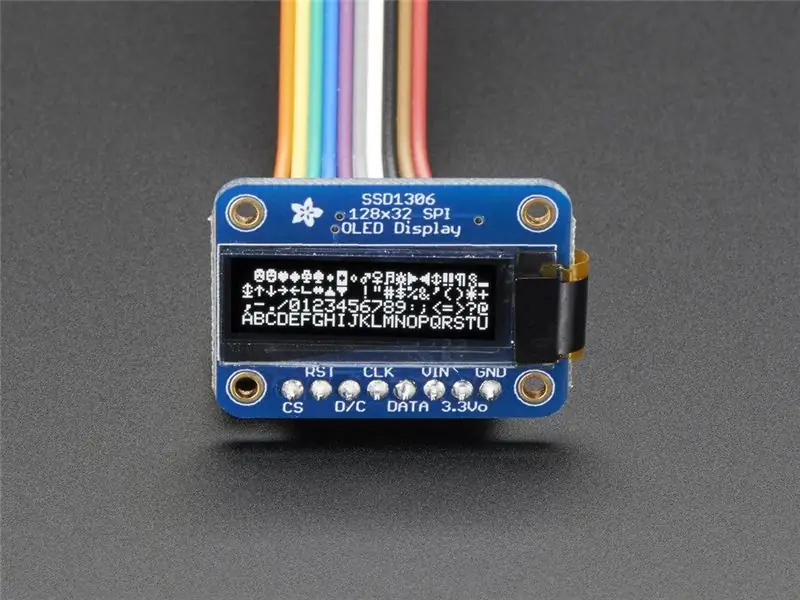

- Pantalla OLED SPI monocromática de 128x32 (lo adivinaste: Adafruit)

- Flip-flop JK doble activado por borde positivo SN74HC109 de Texas Instruments

- Flip-flop JK dual SN74HC112 de activación por borde negativo de Texas Instruments

- Puerta Y cuádruple CD74AC08E de Texas Instruments

- Puerta OR cuádruple CD74AC32E de Texas Instruments

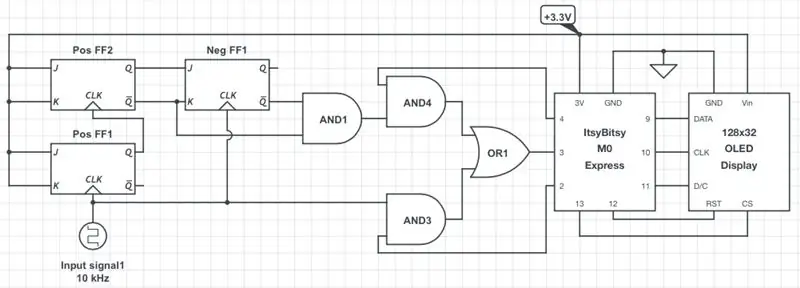

Paso 3: el circuito

La primera figura muestra un esquema simplificado del medidor de frecuencia / trabajo. Se asume la lógica CMOS de 3,3 V en todo momento. En consecuencia, la amplitud de la onda cuadrada de entrada debe estar entre los correspondientes VIH nivel (es decir, 2 V) y 3,3 V. Si no es así, debe ampliarlo o reducirlo en consecuencia. En la mayoría de los casos, bastaría con un simple divisor de voltaje. Si desea diseñar su versión del medidor en un nivel lógico diferente, entonces debe usar otro microcontrolador (MCU), batería y una pantalla que funcione al nivel deseado. Las puertas lógicas y los flip-flops utilizados en este proyecto funcionan con niveles lógicos entre 2 V y 6 V y deberían estar bien en la mayoría de los casos.

Como se muestra, la MCU ItsyBitsy usa los pines 9-13 para comunicarse con la pantalla a través del protocolo SPI del software. El pin de 3V entrega energía a todo el circuito. La clavija de entrada digital 3 acepta la señal analizada, mientras que las clavijas 2 y 4 controlan la fuente de la señal: señal directa que llega a través de la puerta AND3 (frecuencias de entrada bajas) o señal dividida por 4 a través de la puerta AND4 (frecuencias de entrada altas) como se describe en el Paso 2 El código, que se analiza en el siguiente paso, detecta automáticamente el rango de frecuencia entrante y cambia apropiadamente la fuente de la señal.

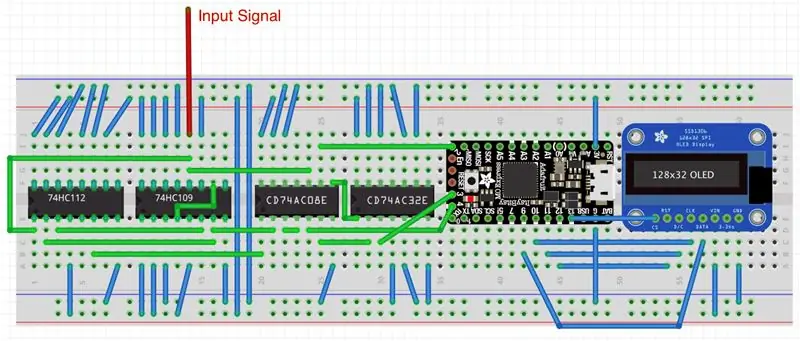

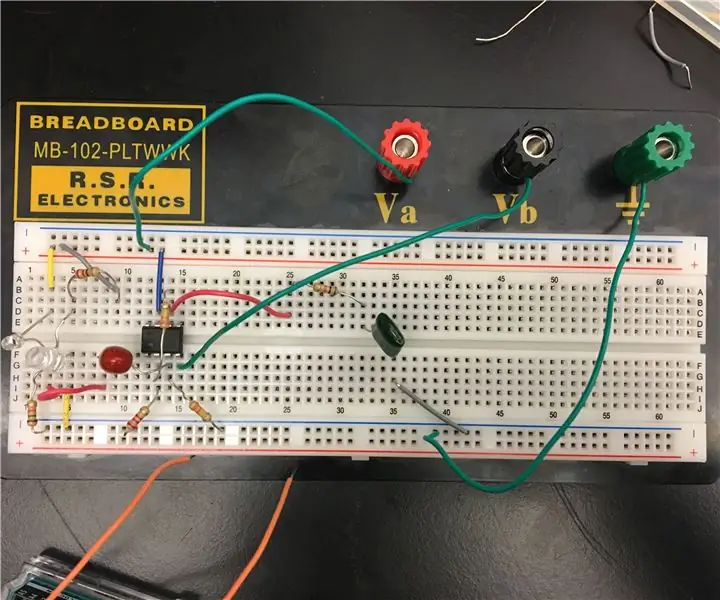

El esquema no muestra la verdadera complejidad de las conexiones de chips digitales. La segunda imagen muestra cómo se vería el proyecto en una placa de pruebas. La señal de entrada llega a través de un cable rojo al pin 2CLK del flip-flop de doble borde positivo. PRECAUCIÓN: Normalmente, todos los pines J y K de este flip-flop deben mantenerse en alto, pero SN74HC109 en particular presenta el pin Kbar, un pin K invertido, en su lugar. ¡Por lo tanto, este pin debe estar conectado a tierra! El primer flip-flop de borde negativo en SN74HC112 tiene su pin 1K y 1J conectado a los pines 1Q y 1Qbar de SN74HC109. El segundo flip-flop en SN74HC112 no se utiliza y sus pines de entrada (2K, 2J, 2CLRbar) están conectados a tierra. Todos los demás pines adicionales PREbar (preestablecido) y CLRbar (claro) en todos los flip-flops deben estar conectados a un nivel lógico alto. Los pines de salida y reloj no utilizados quedan desconectados. De manera similar, los pines de entrada no utilizados en todas las puertas están conectados a tierra, mientras que los pines de salida no utilizados se dejan desconectados. Como mencioné en mi Instructable "Asesino invisible del anillo telefónico", la conexión a tierra de los pines de entrada no utilizados de los chips lógicos elimina las oscilaciones aleatorias y ahorra energía de la batería.

Paso 4: el código y la medición de bajas frecuencias

Naturalmente, toda la acción ocurre en el código vinculado a continuación. Cuando la entrada entrante en el pin 3 cambia de digital bajo a alto, la MCU comienza a contar pulsos de su reloj interno de 48 MHz. Observa el momento de la transición de alto a bajo y continúa la cuenta hasta el siguiente cambio de bajo a alto, cuando reinicia todo el proceso nuevamente. El primer recuento representa el ancho del pulso, mientras que el recuento completo representa el período de la señal. Y ese es todo el secreto.

La CPU toma nota de estas transiciones mediante interrupciones de hardware. El SAMD21 tiene varios relojes; mi código usa TC3 uno. Inicialmente, comencé leyendo la hoja de datos de M0 preparándose para un gran esfuerzo en la codificación del controlador de interrupciones, pero pronto descubrí un código muy relacionado en las publicaciones del Foro Arduino de los usuarios electro_95, MartinL y Rucus cuya contribución es debidamente reconocido. Incorporé y modifiqué su código combinado en el mío; ahorrándome mucho tiempo!

Como mencioné anteriormente, la resolución de la señal está limitada por ~ 106 ciclos de CPU para ejecutar código entre interrupciones. La división digital con preservación del ancho de pulso se encarga de las altas frecuencias. Las bajas frecuencias, por otro lado, plantean otro desafío: dado que el contador de reloj TC3 tiene una longitud de 16 bits, se desborda después de cruzar el límite de 65,536 conteos. Uno puede manejar esta situación agregando una interrupción de desbordamiento, pero eligió una solución diferente: TC3 puede usar un reloj de CPU preescalado (es decir, dividido por software) en lugar del de 48 MHz de hardware. Por lo tanto, si el período de la señal se acerca al límite de desbordamiento, el código puede indicarle a TC3 que use conteos de 24 MHz para el siguiente período y, listo, el contador cae por debajo de 32, 768 conteos. Para frecuencias aún más bajas, se puede indicar al TC3 que cuente pulsos de 12 MHz, etc. El preescalador apropiado se determina automáticamente en función de la frecuencia de la señal, con histéresis, para mantener el contador TC3 dentro del límite de desbordamiento. Como resultado, el extremo inferior del rango del dispositivo es de aproximadamente 43 Hz.

Puede bifurcar el código y usarlo en su proyecto, pero mencione su fuente cuando publique los resultados.

Enlace al código.

Recomendado:

Contador de frecuencia de alta resolución: 5 pasos (con imágenes)

Contador de frecuencia de alta resolución: este instructable muestra un contador de frecuencia recíproco capaz de medir frecuencias rápidamente y con una precisión razonable. Está hecho con componentes estándar y se puede hacer en un fin de semana (me tomó un poco más de tiempo :-)) EDITAR: El código ahora está disponible

Medidor de frecuencia con microcontrolador: 8 pasos

Medidor de frecuencia con microcontrolador: este tutorial simplemente indica cómo calcular la frecuencia de una fuente de pulso usando un microcontrolador. El nivel de alto voltaje de la fuente de pulso es 3.3 V y el bajo es 0V. He usado STM32L476, Tiva launchpad, LCD alfanumérico de 16x2, algunos cables, tablero y 1K resi

Medir su frecuencia cardíaca está en la punta de su dedo: Enfoque de fotopletismografía para determinar la frecuencia cardíaca: 7 pasos

Medir su frecuencia cardíaca está en la punta de su dedo: Enfoque de fotopletismografía para determinar la frecuencia cardíaca: Un fotopletismógrafo (PPG) es una técnica óptica simple y de bajo costo que se usa a menudo para detectar cambios en el volumen de sangre en un lecho de tejido microvascular. Se utiliza principalmente de forma no invasiva para realizar mediciones en la superficie de la piel, normalmente

Cómo hacer un dron usando Arduino UNO »Wiki Ùtil Hacer un cuadricóptero usando un microcontrolador: 8 pasos (con imágenes)

Cómo hacer un dron usando Arduino UNO »Wiki Ùtil Hacer un cuadricóptero usando un microcontrolador: Introducción Visite mi canal de Youtube Un dron es un dispositivo (producto) muy caro de comprar. En este post voy a discutir, ¿cómo lo hago a bajo precio? ¿Y cómo puedes hacer el tuyo así a un precio económico? Bueno, en la India todos los materiales (motores, ESC

Cables plateados personalizados Audio / Digital / Alta frecuencia / GPS: 7 pasos

Cables plateados personalizados Audio / Digital / High Frequency / GPS: Con muchas modificaciones nuevas de audio / video y nuevos dispositivos, tanto audio para ipod como ahora digital para video, debemos conectar nuestros sistemas a nuevos dispositivos con cables más complejos. Algunos muy caros … Estos deben tener componentes & materiales para el proyecto de construcción