Tabla de contenido:

- Paso 1: la etapa de cambio de sesgo

- Paso 2: Resistencia de detección de corriente

- Paso 3: el amplificador de transconductancia

- Paso 4: el amplificador de instrumentación

- Paso 5: etapa de entrada y calibración

- Paso 6: Material avanzado: fuga espectral (CC)

- Paso 7: Material avanzado: fuga espectral (CA)

- Paso 8: Material avanzado: el factor de ganancia teórico

- Paso 9: Cosas avanzadas: el cambio de PA

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:42.

- Última modificación 2025-01-23 14:39.

Me ha interesado hacer un analizador de impedancia biológica para medir la composición corporal y mis búsquedas aleatorias siguieron encontrando un diseño de la clase de instrumentación biomédica de 2015 en la Universidad de Vanderbilt. He trabajado en el diseño y lo he mejorado ligeramente. Me gustaría compartir mis hallazgos con ustedes. Tome lo que puede usar de este "tutorial". Si algo no está claro, sugiera mejoras. Algún día podría escribir mi pensamiento de una forma más coherente, pero por ahora espero que puedas usar lo que veas aquí. (Si crees que puedes escribir esto y mejorar, eres bienvenido)

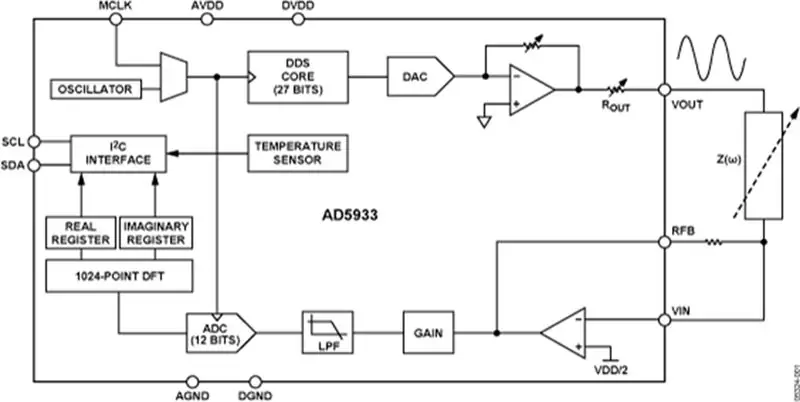

Osito de peluche

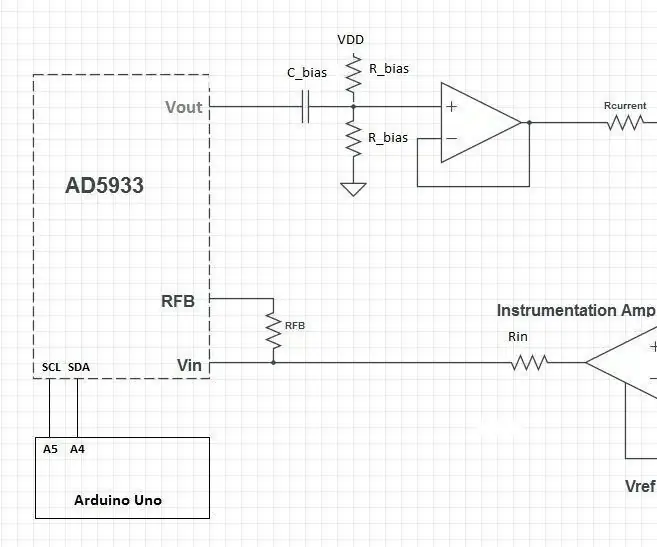

Este diseño consta del chip AD5933 y un front-end analógico personalizado (AFE) para conectar el AD5933 con el cuerpo. El AD5933 luego realiza la medición y los resultados pueden ser procesados por un microcontrolador (por ejemplo, un Arduino).

Si planea usar el Arduino como fuente de alimentación, asegúrese de que los amplificadores operacionales y de instrumentación (amplificadores operacionales y amplificadores de entrada) admitan los llamados voltajes de "suministro único" y tengan especificaciones de riel a riel.

(A continuación, usaré una fuente de alimentación (de un Arduino) de 5V y la configuración de Rango 1 en el AD5933).

Paso 1: la etapa de cambio de sesgo

La primera parte del AFE es una etapa de redistribución. La señal de voltaje de salida no está centrada en el medio del rango de voltaje de suministro (VDD / 2). Esto se corrige usando un capacitor para bloquear la parte de CC de la señal y enviándola a través de un divisor de voltaje para agregar una compensación de CC a la señal.

Las dos resistencias de redistribución pueden tener cualquier valor siempre que sean iguales. El valor específico del límite tampoco es importante.

La etapa de redistribución funciona como un filtro de paso alto y, por lo tanto, tiene una frecuencia de corte:

f_c = 1 / (2 * pi * (0.5 * R) * C)

Asegúrese de que la frecuencia de corte esté algunas décadas por debajo de la frecuencia mínima que planea usar. Si planea usar 1kHz en su aplicación, debe optar por límites y valores de resistencia que le darán una frecuencia de corte del orden de 1-10 Hz.

La última parte de esta etapa es un amplificador operacional configurado para ser un seguidor de voltaje. Esto es para asegurarse de que los valores de la resistencia no interfieran con la siguiente etapa.

Paso 2: Resistencia de detección de corriente

La primera parte de la siguiente etapa es la resistencia de detección de corriente. La corriente a través de esta resistencia será la misma corriente que el amplificador intentará mantener a través del cuerpo. Asegúrese de que la corriente cumpla con las normas de seguridad IEC6060-1 *:

Por debajo de las frecuencias de 1 kHz, se permite un máximo de 10 microAmps (RMS) a través del cuerpo. A frecuencias superiores a 1 kHz, la siguiente ecuación proporciona la corriente máxima permitida:

Corriente CA máxima <(frecuencia mínima en kHz) * 10 microAmps (RMS)

La relación entre la amplitud máxima de una señal de CA y su valor RMS es: Peak = sqrt (2) * RMS. (10 microAmps RMS corresponden a 14 microAmps de amplitud pico)

Usando la Ley de Ohmios en la resistencia, podemos calcular el valor de la resistencia que cumplirá con el estándar de seguridad. Usamos el voltaje de excitación del AD5933 y el valor de corriente máxima:

U = R * I => R = U / I

P.ej. usando la configuración de Rango 1 Upeak = 3V / 2 = 1.5V (o 1V @ 3.3V)

Usando el valor pico de 14 microAmp de arriba, obtengo un valor de resistencia de al menos 107kOhms

Referencias:

* Dispositivos analógicos: "Diseño de circuito de bio-impedancia para sistemas desgastados por el cuerpo"

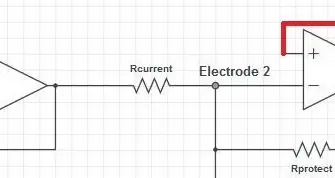

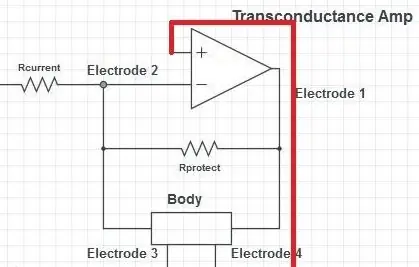

Paso 3: el amplificador de transconductancia

Después del resistor de detección de corriente hay un amplificador operacional en una configuración de retroalimentación negativa. Esta es la denominada configuración Load-in-the-Loop. El terminal de entrada positivo del amplificador operacional está conectado a un voltaje VDD / 2. El amplificador operacional ahora intentará ajustar su salida en la dirección opuesta a la señal de excitación de modo que el voltaje en el terminal negativo sea igual a VDD / 2. Esto producirá un potencial oscilante empujando y tirando de la corriente a través del cuerpo.

La corriente extraída del terminal negativo del amplificador operacional es prácticamente cero. Por lo tanto, toda la corriente a través de la resistencia de detección de corriente tiene que fluir a través del cuerpo. Este es el mecanismo que hace que esta configuración sea un amplificador de transconductancia (también llamado fuente de corriente controlada por voltaje, VCCS).

El amplificador operacional solo puede mantener la corriente si la impedancia del cuerpo no es demasiado alta. De lo contrario, la salida del amplificador operacional se alcanzaría al máximo con el voltaje de suministro (0 o 5 V). El rango de voltaje máximo que se puede mantener es VDD / 2 + Upeak (2,5 + 1,5 V = suministro de 4 V a 5 V). Los márgenes de voltaje del amplificador operacional deben restarse de este valor, pero si el amplificador operacional tiene especificaciones de riel a riel, solo sería una pequeña cantidad. Por lo tanto, la impedancia máxima que puede manejar el amplificador operacional es:

Z <(VDD / 2 + pico) / Imax

(En mi configuración Z <4V / 14 microAmps = 285 kOhms, el deseo es suficiente para cubrir el rango de impedancia del cuerpo)

La resistencia protectora tiene un valor muy grande (1-1,5 MOhms) en comparación con el cuerpo (aproximadamente 100kOhms) y para todas las operaciones normales no consumirá ninguna corriente notable y la impedancia de la conexión en paralelo está dominada por la impedancia del cuerpo. Si la impedancia del cuerpo aumentara (por ejemplo, las almohadillas se aflojan), la corriente puede pasar a través de la resistencia y el máximo del amplificador operacional no crearía voltajes desagradables en las almohadillas.

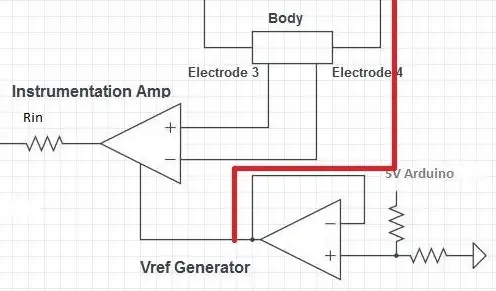

Paso 4: el amplificador de instrumentación

La siguiente etapa es el amplificador de instrumentación (en amperios) que mide el voltaje en todo el cuerpo. El voltaje en todo el cuerpo oscila alrededor de 0 V, pero el AD5933 necesita que el voltaje de entrada esté en un rango positivo. Por lo tanto, el amplificador de entrada agrega una compensación de CC de VDD / 2 a la señal de voltaje medida.

La referencia VDD / 2 es generada por un divisor de voltaje. Se puede utilizar cualquier resistencia de valor siempre que sean iguales. El divisor de voltaje está separado de la impedancia del resto del circuito por un seguidor de voltaje. La salida del seguidor de voltaje se puede reenviar tanto al amplificador de entrada como al amplificador de transconductancia.

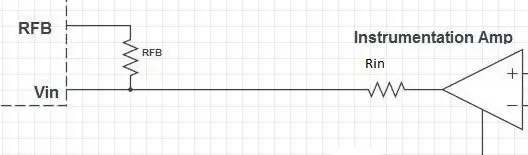

Paso 5: etapa de entrada y calibración

La etapa de entrada del AD5933 contiene un amplificador operacional en configuración de retroalimentación negativa. Hay dos resistencias: una en serie (Rin) y otra en paralelo (RFB). La ganancia del amplificador operacional viene dada por

A = - RFB / Rin

Las ganancias del amplificador operacional de entrada y del amplificador de entrada (y PGA) deben asegurarse de que la señal que ingresa al ADC del AD5933 esté siempre dentro de 0V y VDD.

(Yo uso una ganancia unitaria en amperios y valores de resistencia que darán aproximadamente A = 0.5)

Dentro del AD5933, el ADC convertirá la señal de voltaje en una señal digital. El rango de voltaje de 0V a VDD se convierte al rango digital 0-128 (2 ^ 7). (La documentación no es clara sobre esto, pero un examen detenido de las tramas en [1] y algunos experimentos de mi parte lo confirman).

Dentro del módulo DFT hay otra escala de 256 (1024/4, ver [1]) antes de que el resultado se guarde en el registro real e imaginario.

Siguiendo la señal de voltaje a través del AFE, en el ADC y usando los factores de escala mencionados anteriormente, es posible estimar que el factor de ganancia es:

g = (VDD * R actual * Rin) / (256 * PGA * Upeak * RFB * 2 ^ 7)

Es posible que aún sea necesario realizar alguna calibración, así que tenga en cuenta algunos efectos que no forman parte de este modelo matemático, por lo que debe medir el valor de ganancia real midiendo componentes de impedancia conocida, como resistencias. (g = Z / mag, ver más abajo)

La impedancia ahora se puede calcular mediante

Z = g * mag

mag = sqrt (real ^ 2 + imaginario ^ 2)

PA = arctan2 (real, imaginario) - deltaPA

Probablemente sea necesario calibrar el PA y hay un cambio de fase sistemático en función de la frecuencia en el AD5933. deltaPA probablemente será una función lineal de frecuencia.

La resistencia y la reactancia ahora se pueden calcular mediante

R = Z * cos (PA)

X = Z * sin (PA)

Referencias: [1] Leonid Matsiev, "Mejora del rendimiento y la versatilidad de sistemas basados en detectores DFT de frecuencia única como AD5933", Electronics 2015, 4, 1-34; doi: 10.3390 / electrónica4010001

Paso 6: Material avanzado: fuga espectral (CC)

La señal que ponemos en el AD5933 es un voltaje / corriente como función del tiempo, pero nuestro principal interés es la impedancia como función de la frecuencia. Para convertir entre el dominio del tiempo y el dominio de la frecuencia, necesitamos tomar la transformada de Fourier de la señal en el dominio del tiempo. El AD5933 tiene un módulo de transformada discreta de Fourier (DFT) incorporado. A bajas frecuencias (por debajo de aproximadamente 10 kHz), la construcción en DFT está influenciada por aliasing y fugas espectrales. En [1] repasa las matemáticas de cómo corregir la fuga espectral. La esencia de esto es calcular cinco (más dos) constantes para cada paso de frecuencia en el barrido. Esto se puede hacer fácilmente, p. Ej. por el Arduino en software.

La fuga se presenta en dos formas: una fuga de CC que es de naturaleza aditiva y una fuga de CA que es de naturaleza multiplicativa.

La fuga de CC se debe al hecho de que la señal de voltaje en el ADC no oscila alrededor de 0 V sino alrededor de VDD / 2. Un nivel de CC de VDD / 2 debe corresponder a una lectura de CC digital de aproximadamente 64 (delta designado en [1]).

Los pasos para corregir la fuga espectral de CC:

1) Calcule el factor de envolvente E para la frecuencia actual.

2) Calcule los dos factores de ganancia GI (real) y GQ (imaginario)

3) Reste delta * GI del valor del registro real y delta * GQ del valor del registro imaginario

Referencias:

[1] Leonid Matsiev, "Mejorar el rendimiento y la versatilidad de los sistemas basados en

Detectores DFT de frecuencia única como AD5933 , Electronics 2015, 4, 1-34; doi: 10.3390 / electronics4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "Medidor de impedancia de amplio rango de frecuencia simple basado en el circuito integrado AD5933", Metrol. Meas. Syst., Vol. XXII (2015), núm. 1, págs. 13-24.

Paso 7: Material avanzado: fuga espectral (CA)

Al igual que la fuga de CC, la fuga de CA se puede corregir matemáticamente. En [1] la resistencia y la reactancia se denominan A * cos (phi) y A * sin (phi) respectivamente, donde A corresponde a la magnitud de la impedancia y phi corresponde al ángulo de fase (PA).

Los pasos para corregir la fuga espectral de CA:

1) Calcule el factor de envolvente E (no el mismo que para CC) para la frecuencia actual.

2) Calcule los tres factores a, by d. (valores aproximados a frecuencias más altas: a = d = 256 yb = 0)

3) La resistencia (Acos (phi)) y la reactancia (Asin (phi)) ahora se pueden calcular en unidades digitales

Referencias: [1] Leonid Matsiev, "Mejora del rendimiento y la versatilidad de sistemas basados en detectores DFT de frecuencia única como AD5933", Electronics 2015, 4, 1-34; doi: 10.3390 / electrónica4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "Medidor de impedancia de amplio rango de frecuencia simple basado en el circuito integrado AD5933", Metrol. Meas. Syst., Vol. XXII (2015), núm. 1, págs. 13-24.

Paso 8: Material avanzado: el factor de ganancia teórico

Dado el modelado matemático de la DFT, también debería ser posible modelar matemáticamente todo el AFE. Matemáticamente, la señal de voltaje se puede describir mediante una función sinusoidal con una frecuencia fija dada, un desplazamiento de CC y una oscilación de CA con una amplitud máxima. La frecuencia no cambia durante un paso de frecuencia. Como el factor de ganancia solo cambia la magnitud de la impedancia y no el PA, aquí no nos preocuparemos por ningún cambio de fase inducido en la señal.

Aquí hay un breve resumen de la señal de voltaje a medida que se propaga a través del AFE:

1) Después de la etapa de redistribución, la amplitud de CA sigue siendo Upeak = 1.5V (1V @ VDD = 3.3V) y el DC offcet se ha cambiado a VDD / 2.

2) En la resistencia de detección de corriente, el voltaje sigue siendo el mismo que en la etapa anterior …

3)… pero debido al voltaje oscilante del amplificador operacional, las oscilaciones de CA tienen un tamaño de Z * Upeak / Rcurrent. (La compensación de CC se cancela con el voltaje de referencia de los amplificadores operacionales de VDD / 2, el punto de pivote del balancín, y se convierte en una tierra virtual en esta parte del circuito)

4) La unidad en amplificador agrega la compensación de CC de VDD / 2 nuevamente y reenvía la señal a la etapa de entrada del AD5933

5) El amplificador operacional en la etapa de entrada tiene una ganancia de A = -RFB / Rin y, por lo tanto, la amplitud de CA se convierte en (Z * Upeak / Rcurrent) * (RFB / Rin)

6) Justo antes del ADC hay un amplificador de ganancia programable (PGA) con dos configuraciones, una ganancia de 1 o 5. Por lo tanto, la señal de voltaje en el ADC se convierte en: PGA * (Z * Upeak / Rcurrent) * (RFB / Rin)

El ADC convierte la señal v (t) en una señal digital x (t) = u (t) / VDD * 2 ^ 7 con una precisión de 12 bits.

La magnitud A está conectada a la impedancia Z por el factor de ganancia, k, como A = k * Z y tiene un valor aproximado de k = PGA * Upeak * RFB * 2 ^ 7 / (VDD * Rcurrent * Rin).

Si desea trabajar con gain-faktor en lugar de g = 1 / k y Z = g * A.

Paso 9: Cosas avanzadas: el cambio de PA

En [2] encuentran un cambio sistemático en el PA en función de la frecuencia. Esto se debe a un retardo de tiempo entre el DAC donde se genera la señal de excitación y el DFT donde la señal entrante necesita convolucionarse con la señal saliente.

El cambio se caracteriza por el número de ciclos de reloj en el que la señal tiene un retraso entre el DAC y el DFT internamente en el AD5933.

Referencias: [1] Leonid Matsiev, "Mejora del rendimiento y la versatilidad de los sistemas basados en detectores DFT de frecuencia única como el AD5933", Electronics 2015, 4, 1-34; doi: 10.3390 / electrónica4010001

[2] Konrad Chabowski, Tomasz Piasecki, Andrzej Dzierka, Karol Nitsch, "Medidor de impedancia de amplio rango de frecuencia simple basado en el circuito integrado AD5933", Metrol. Meas. Syst., Vol. XXII (2015), núm. 1, págs. 13-24.

Recomendado:

Análisis de LTE Cat.M1 PSM (modo de ahorro de energía): 4 pasos

Análisis de LTE Cat.M1 PSM (modo de ahorro de energía): en el artículo anterior, hemos discutido cómo configurar el ciclo activo / inactivo usando PSM. Consulte el artículo anterior para obtener explicaciones sobre la configuración de hardware y PSM y el comando AT. (Enlace: https://www.instructables.com/id/What-Is-a-PSMPow…Ac

Análisis de datos de temperatura / humedad usando Ubidots y Google-Sheets: 6 pasos

Análisis de datos de temperatura / humedad usando Ubidots y Google-Sheets: En este tutorial, mediremos diferentes datos de temperatura y humedad usando un sensor de temperatura y humedad. También aprenderá a enviar estos datos a Ubidots. Para que pueda analizarlo desde cualquier lugar para diferentes aplicaciones. También enviando

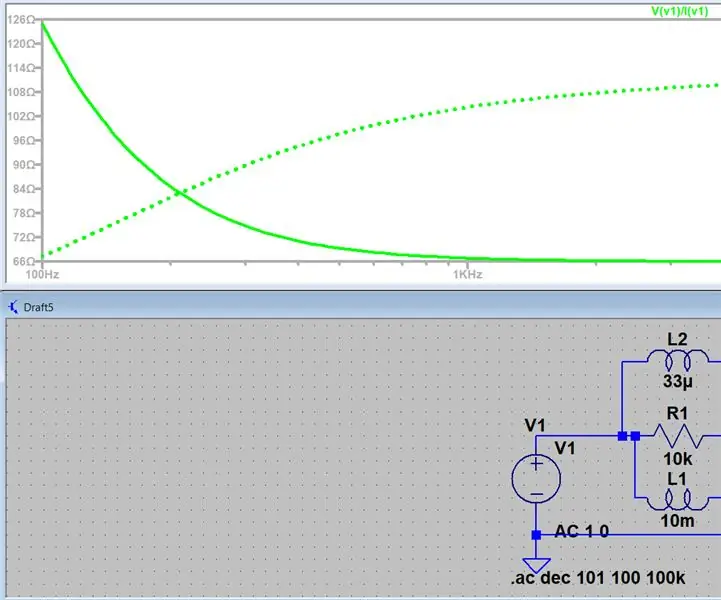

Medición de impedancia con LTspice: 4 pasos

Midiendo la impedancia usando LTspice: Hola a todos, esta va a ser una introducción simple para generar un barrido de CA de un circuito y encontrar la impedancia en un punto dado, esto apareció varias veces en mis cursos y fue muy difícil para mí encontrar alguno. forma de hacerlo en línea, así que

Análisis de sentimiento de Twitter con Raspberry Pi: 3 pasos (con imágenes)

Análisis de sentimientos de Twitter con Raspberry Pi: ¿Qué es el análisis de sentimientos y por qué debería preocuparte por él? El análisis de sentimientos es el proceso de determinar el tono emocional detrás de una serie de palabras, que se utiliza para comprender las actitudes, opiniones y emociones expresadas. dentro de un

Análisis del sistema Bluetooth de Windows: un enfoque SensorTag: 7 pasos (con imágenes)

Análisis del sistema Bluetooth de Windows: un enfoque de SensorTag: A continuación, haré un análisis del sistema operativo (SO) Windows desde el punto de vista de la comunicación con dispositivos Bluetooth de baja energía - en nuestro caso con diferentes tipos de SensorTags: Thunderboard React, Thunderboard Sense (b