Tabla de contenido:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:41.

- Última modificación 2025-01-23 14:39.

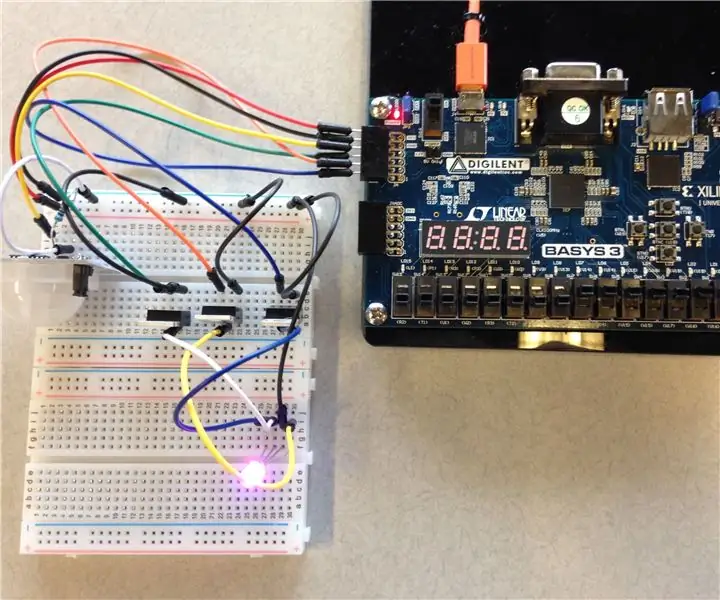

Nuestro objetivo con este proyecto era crear algo que ahorrara energía y recursos financieros a las comunidades. Las luces de la calle activadas por movimiento harían ambas cosas. En todo el país se desperdicia energía en las luces de las calles alumbrando las calles que están vacías. Nuestro sistema de alumbrado público garantiza que las luces estén encendidas solo cuando sea necesario, lo que ahorra a las comunidades una gran cantidad de dólares. Usando sensores de movimiento, el sistema enciende las luces solo cuando hay autos presentes. También para la seguridad de los peatones, implementamos un botón de anulación que enciende todas las luces de la calle. Los siguientes pasos lo guiarán a través de cómo diseñamos y construimos nuestro modelo reducido del proyecto utilizando Vivado y una placa Basys 3.

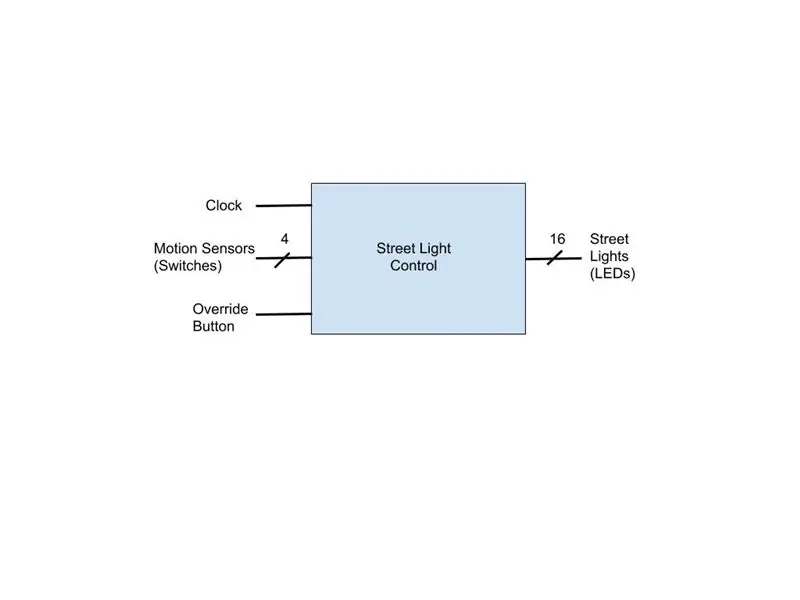

Paso 1: Caja negra del sistema

Comenzamos este proyecto dibujando un diagrama simple de caja negra. Un diagrama de caja negra simplemente muestra las entradas y salidas que nuestro sistema requiere para completar todos los procesos necesarios. Intentamos mantener nuestro diseño lo más simple y básico posible. Nuestras tres entradas del sistema incluían un bus de sensores de movimiento (4 para nuestro modelo reducido), un botón de anulación de peatones y una entrada de reloj. En el otro lado, nuestra única salida es un bus de luces LED que representan nuestras farolas. Para este modelo utilizamos un escenario de 16 farolas simplemente porque ese es el número máximo de salidas LED integradas en la placa Basys 3. Finalmente, usando este diagrama pudimos crear nuestro proyecto Vivado, fuente y archivos de restricción con entradas y salidas apropiadas.

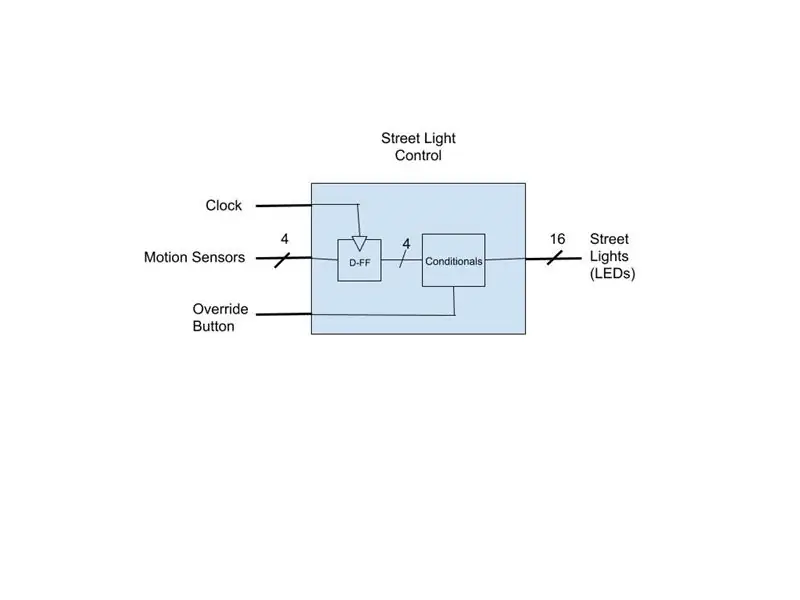

Paso 2: componentes

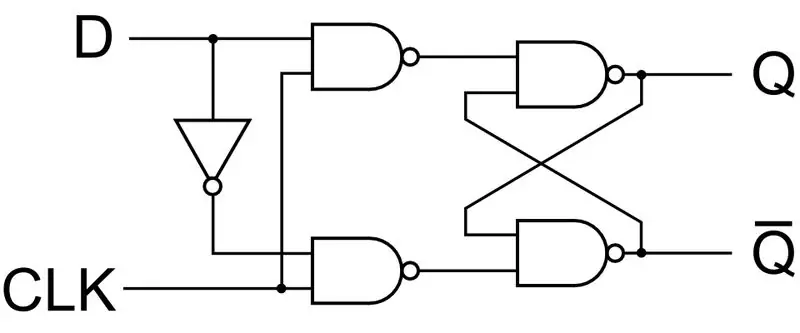

En este paso profundizamos examinando los componentes que componen nuestro diagrama de caja negra. Nuestro primer componente es un archivo fuente VHDL que contiene flip-flops D. Los flip-flops D simplemente toman cualquier señal que se les esté ingresando desde los sensores en el borde ascendente del reloj y retienen esos datos hasta el siguiente borde ascendente. Esto evita que nuestros sensibles sensores de movimiento provoquen que los LED de salida "parpadeen". Además, colocamos un solo flip-flop D en la señal de entrada del botón para mantener los LED encendidos durante aproximadamente 5-7 segundos después de presionar el botón. También pasamos esto a través de un divisor de reloj.

la entidad clk_div2 es Puerto (clk: en std_logic; sclk: fuera de std_logic); end clk_div2;

arquitectura my_clk_div de clk_div2 es

cuenta_máx constante: entero: = (300000000); señal tmp_clk: std_logic: = '0'; begin my_div: process (clk, tmp_clk) variable div_cnt: integer: = 0; comenzar si (aumento_de_borde (clk)) luego si (div_cnt = MAX_COUNT) entonces tmp_clk <= no tmp_clk; div_cnt: = 0; más div_cnt: = div_cnt + 1; terminara si; terminara si; sclk <= tmp_clk; finalizar el proceso my_div; end my_clk_div;

Nuestro componente final en este diagrama es un archivo fuente de comportamiento VHDL que contiene condicionales para las salidas basadas en la configuración de las señales de entrada.

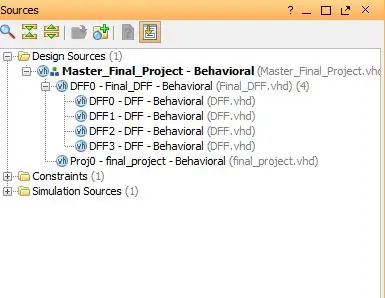

Paso 3: D Flip-Flops

Los cuatro flip-flops conectados a las señales de entrada son esenciales para la funcionalidad de nuestro sistema. Como se dijo anteriormente, con sensores de movimiento sensibles y un botón de anulación, los flip-flops usan pestillos para emitir solo nuestra señal de entrada en el borde ascendente del reloj. Esta lógica secuencial significa que nuestras luces de la calle pueden permanecer encendidas durante un período de tiempo determinado después de ser activadas por un movimiento rápido. La codificación de un D-Flip Flop es bastante simple:

beginprocess (CLK) begin if rising_edge (CLK) then Q <= D; terminara si; proceso finalizado;

Todo se puede compilar en una sola declaración if. Una vez que tuvimos esta pieza, creamos un archivo fuente VHDL estructural que contiene los cuatro flip-flops necesarios:

begin DFF0: mapa de puertos DFF (CLK => CLK, D => D (0), Q => Q (0)); DFF1: mapa de puertos DFF (CLK => CLK, D => D (1), Q => Q (1)); DFF2: mapa de puertos DFF (CLK => CLK, D => D (2), Q => Q (2)); DFF3: mapa de puertos DFF (CLK => CLK, D => D (3), Q => Q (3));

end Behavioral;

Esto ayuda a mantener nuestro archivo estructural maestro donde reunimos todos los componentes del sistema mucho más limpios y organizados.

Paso 4: condicionales

Para mantener nuestro código compacto y eficiente, escribimos todos nuestros condicionales en una sola declaración de caso. Para nuestro modelo reducido, teníamos 16 posibles configuraciones de salida de LED, ya que cada sensor de movimiento es responsable de un grupo de 4 LED.:

caso NMS es cuando "1111" => LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED LED <= "1111111111111111"; caso final;

Paso 5: restricciones

Para establecer correctamente sus entradas y salidas usando Vivado, debe implementar un archivo de restricción que indique todos los puertos, botones, LED y relojes que se están utilizando.

set_property PACKAGE_PIN W5 [get_ports CLK] set_property IOSTANDARD LVCMOS33 [get_ports CLK]

set_property PACKAGE_PIN U16 [get_ports {LED [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [0]}] set_property PACKAGE_PIN E19 [get_ports {LED [1]}] set_property IOSTANDARD LVCMOS33 [get_ports PACKAGE [1]}] U19 [get_ports {LED [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [2]}] set_property PACKAGE_PIN V19 [get_ports {LED [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [3]}] set_property PACKAGE_PIN W get_ports {LED [4]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [4]}] set_property PACKAGE_PIN U15 [get_ports {LED [5]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [5]}] set_property PACKAGE_PIN U14 [LED [6]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [6]}] set_property PACKAGE_PIN V14 [get_ports {LED [7]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [7]}] set_property PACKAGE_PIN LED V13 [get_ports 8]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [8]}] set_property PACKAGE_PIN V3 [get_ports {LED [9]}] set_property IO ESTÁNDAR LVCMOS33 [get_ports {LED [9]}] set_property PACKAGE_PIN W3 [get_ports {LED [10]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [10]}] set_property PACKAGE_PIN U3 [get_ports {LED [11]}] conjunto LVCMOS33 [get_ports {LED [11]}] set_property PACKAGE_PIN P3 [get_ports {LED [12]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [12]}] set_property PACKAGE_PIN N3 [get_ports {LED [13]}] set_property IOSTANDARD_ LVCMOS33 {LED [13]}] set_property PACKAGE_PIN P1 [get_ports {LED [14]}] set_property IOSTANDARD LVCMOS33 [get_ports {LED [14]}] set_property PACKAGE_PIN L1 [get_ports {LED [15]}] set_property IOSTANDARD LVCMOS33 [get_ports [15]}]

set_property PACKAGE_PIN U18 [get_ports BTN] set_property IOSTANDARD LVCMOS33 [get_ports BTN]

set_property PACKAGE_PIN A14 [get_ports {MS [0]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [0]}] set_property PACKAGE_PIN A16 [get_ports {MS [1]}] set_property IOSTANDARD LVCMOS33 [get_ports PACKAGE MS [1]}] B15 [get_ports {MS [2]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [2]}] set_property PACKAGE_PIN B16 [get_ports {MS [3]}] set_property IOSTANDARD LVCMOS33 [get_ports {MS [3]}]

Paso 6: archivo de origen principal

En este archivo principal reunimos todos los archivos fuente de componentes mencionados anteriormente. Este archivo funciona como código estructural que reúne los componentes dispares.

la entidad Master_Final_Project es Puerto (BTN: en STD_LOGIC; CLK: en STD_LOGIC; MS: en STD_LOGIC_VECTOR (3 hacia abajo 0); LED: hacia fuera STD_LOGIC_VECTOR (15 hacia abajo 0)); end Master_Final_Project;

arquitectura El comportamiento de Master_Final_Project es

el componente final_project es Port (--CLK: en STD_LOGIC; NMS: en STD_LOGIC_VECTOR (3 hacia abajo 0); BTN: en STD_LOGIC; --sw: en STD_LOGIC_Vector (1 hacia abajo 0); LED: hacia STD_LOGIC_VECTOR (15 hacia abajo 0)); componente final;

componente Final_DFF es

Puerto (CLK: en STD_LOGIC; D: en STD_LOGIC_Vector (3 hacia abajo 0); Q: hacia fuera STD_LOGIC_Vector (3 hacia abajo 0)); componente final;

señal DFF02proj30: STD_LOGIC;

señal DFF12proj74: STD_LOGIC; señal DFF22proj118: STD_LOGIC; señal DFF32proj1512: STD_LOGIC;

empezar

DFF0: Mapa de puertos Final_DFF (CLK => CLK, D (0) => MS (0), D (1) => MS (1), D (2) => MS (2), D (3) => MS (3), Q (0) => DFF02proj30, Q (1) => DFF12proj74, Q (2) => DFF22proj118, Q (3) => DFF32proj1512); Proj0: mapa de puertos del proyecto final (NMS (0) => DFF02proj30, NMS (1) => DFF12proj74, NMS (2) => DFF22proj118, NMS (3) => DFF32proj1512, BTN => BTN, LED => LED); end Behavioral;

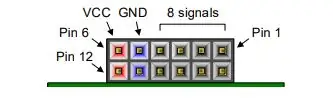

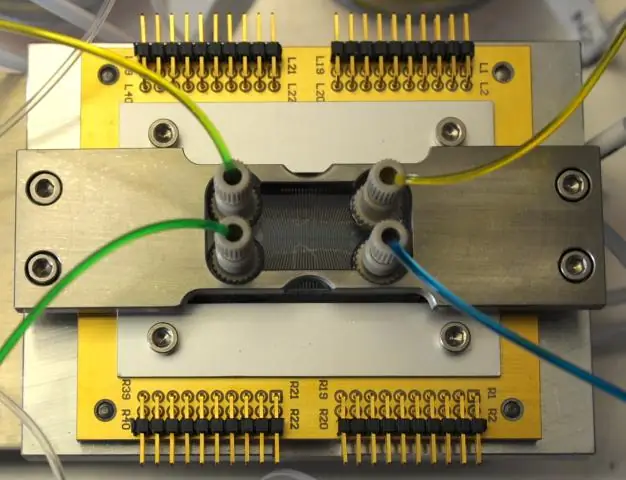

Paso 7: Montaje

El montaje de hardware para este proyecto es mínimo. Las únicas piezas requeridas son las siguientes:

1. Tablero Basys 3 (1)

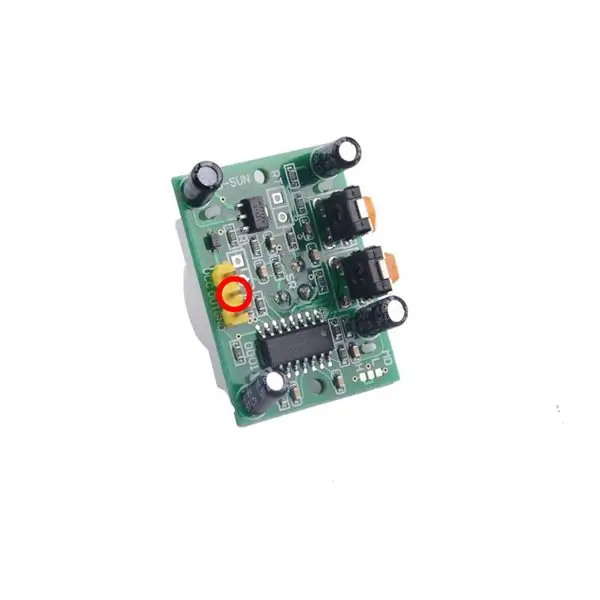

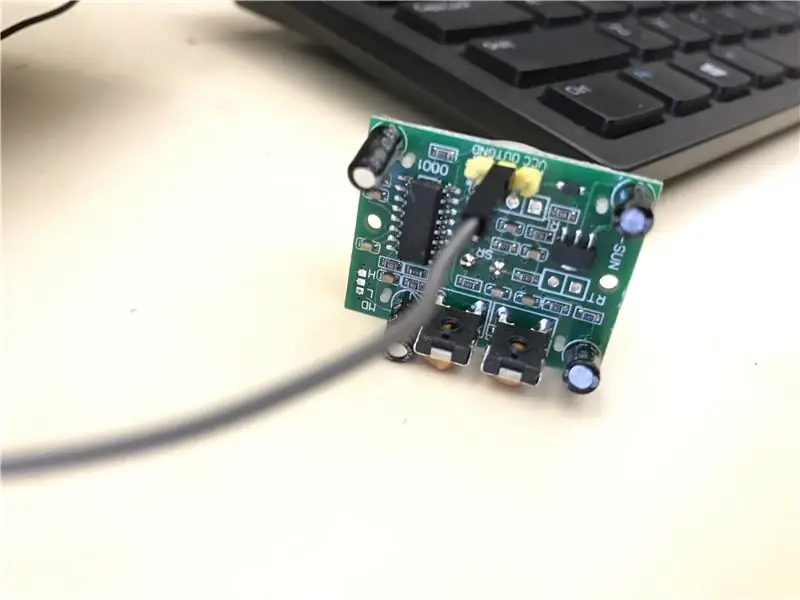

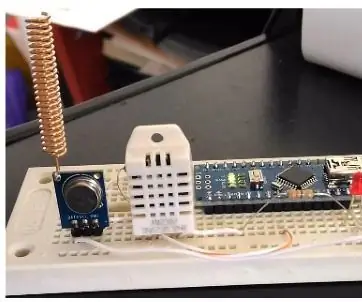

2. Sensores de movimiento económicos que se pueden encontrar en Amazon aquí. (4)

3. Clientes potenciales de hombre a mujer (4)

Montaje:

1. Conecte 4 cables macho a los puertos JB 1-4 del cabezal PMod (consulte la figura).

2. Conecte los extremos hembra a la clavija de salida de cada sensor de movimiento.

Paso 8: carga del programa

Ahora estamos listos para cargar el archivo fuente maestro VHDL en la placa Basys 3. Asegúrese de ejecutar la síntesis, la implementación y generar la verificación del flujo de bits para detectar posibles errores. Si todo se ejecuta correctamente, abra el administrador de hardware y programe el dispositivo Basys 3. ¡Tu proyecto ya está completo!

Recomendado:

Alas de cosplay activadas por movimiento usando Circuit Playground Express - Parte 1: 7 pasos (con imágenes)

Alas de cosplay activadas por movimiento usando Circuit Playground Express - Parte 1: Esta es la primera parte de un proyecto de dos partes, en el que les mostraré mi proceso para hacer un par de alas de hadas automatizadas. mecánica de las alas, y la segunda parte es hacer que se pueda usar y agregar las alas

Luces activadas por movimiento: 5 pasos

Luces activadas por movimiento: esta guía le mostrará cómo usar un FPGA para crear una luz activada por sensor de movimiento de diferentes colores mientras haya movimiento. Los niveles de rojo, azul y verde se controlan fijando un valor a cada color individual. Este proyecto w

¿Cómo medir correctamente el consumo de energía de los módulos de comunicación inalámbrica en la era de bajo consumo de energía ?: 6 pasos

¿Cómo medir correctamente el consumo de energía de los módulos de comunicación inalámbrica en la era del bajo consumo de energía ?: El bajo consumo de energía es un concepto extremadamente importante en la Internet de las cosas. La mayoría de los nodos de IoT deben funcionar con baterías. Solo midiendo correctamente el consumo de energía del módulo inalámbrico podemos estimar con precisión cuánta batería i

LEIDS - Sensor de puerta IOT de bajo consumo energético: 8 pasos (con imágenes)

LEIDS - Sensor de puerta IOT de baja energía: ¿Qué es LEIDS? LEIDS es un sensor IOT que se basa en el ESP8266. Este sensor hace uso de esta placa, un circuito de cierre suave, un interruptor de lengüeta y algunos imanes para crear un sensor de puerta que le enviará una alerta cuando la puerta se abra y cierre

Computadora de bajo consumo energético: 9 pasos

Computadora con uso eficiente de la energía: hay innumerables instructivos y artículos sobre cómo construir su propia PC en la web y en forma impresa. Sin embargo, no hay tantas guías para construir una PC que sea energéticamente eficiente. A lo largo de este instructivo, te daré algunos consejos sobre cómo sel