Tabla de contenido:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:41.

- Última modificación 2025-01-23 14:39.

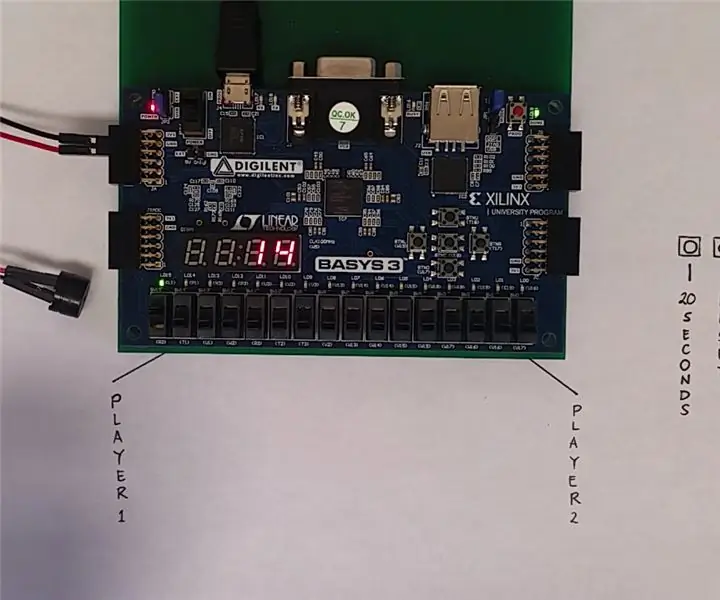

El sistema de timbre competitivo diseñado en este proyecto funciona de manera similar a los sistemas de timbre utilizados en las competencias regionales y nacionales de Science Bowl. Este proyecto se inspiró en mi participación con el equipo de cuencos de ciencias de mi escuela secundaria durante tres años. Siempre hemos tenido el deseo de recrear el sistema de timbre de bloqueo con un temporizador de 5 y 20 segundos.

Para dar algunos antecedentes sobre el sistema de timbre, los timbres del cuenco de ciencia están programados para ingresar un máximo de 8 jugadores (con 8 timbres separados). Una vez que se ha presionado un timbre, el timbre de la primera persona se encenderá para indicar qué jugador recibe la pregunta. El resto de los jugadores quedará "bloqueado", lo que significa que sus timbres no responderán hasta que el moderador reinicie el sistema de timbre.

Después de que el moderador lea las preguntas, presionará un botón para iniciar el temporizador de cuenta regresiva que se mostrará en la pantalla de siete segmentos. Después de una pregunta "lanzada", el moderador puede presionar el botón derecho para comenzar la cuenta regresiva a partir de 5 segundos. Mientras tanto, después de una pregunta de "bonificación", el moderador puede presionar el botón izquierdo para iniciar la cuenta regresiva desde 20 segundos. Una vez que el temporizador llega a cero, un timbre de sonido indicará que el jugador se ha quedado sin tiempo.

Para reiniciar el sistema y el temporizador de cuenta regresiva, el moderador puede presionar el botón central. Para restablecer el mecanismo de bloqueo y los LED del jugador, los interruptores para el jugador 1 y el jugador 2 deben estar en bajo.

Paso 1: Materiales

Necesitará lo siguiente:

- Placa Basys3 (o placa FPGA equivalente)

- Cable USB micro-B

- Altavoz (usé un altavoz pasivo)

- 2 hilos

- Software para implementar en la FPGA (yo usé Vivado)

- Archivo del sistema de zumbador competitivo

Paso 2: Diagrama de caja negra

El diagrama de caja negra muestra las entradas y salidas que se utilizarán en este sistema de timbre.

ENTRADAS:

player1, player2 Estas entradas están conectadas a dos interruptores en la placa Basys3. Por conveniencia, se utilizarán los interruptores más a la izquierda y a la derecha.

reiniciar El botón central se utilizará para representar el botón de reinicio.

count_down_20_sec El botón izquierdo se utilizará para representar el botón del temporizador de 20 segundos.

count_down_5_sec El botón derecho se utilizará para representar el botón del temporizador de 20 segundos. Para asegurarse de que se inicie el temporizador de 20 segundos y de 5 segundos, mantenga presionado el botón hasta que la pantalla de siete segmentos muestre el temporizador.

CLK La placa FPGA generará un reloj que se ejecuta con una frecuencia de 10 ns.

SALIDAS:

altavoz La salida del altavoz está conectada a un zumbador o altavoz externo. Tendrá que conectar el altavoz a los puertos pmod JA de la placa Basys3. Este paso se describirá a continuación.

speaker_LED Esta salida está conectada a un LED en el centro de la placa, y solo indicará cuando la salida de altavoz de la FPGA es alta. Puede usar esto para probar su altavoz externo. Tenga en cuenta que es posible que algunos de los puertos pmod no funcionen bien, por lo que puede probar diferentes y usar el LED para verificar si el altavoz debería estar encendido.

SEGMENTOS Esta salida está conectada a los ocho segmentos individuales en la pantalla de siete segmentos, incluido el punto decimal.

DISP_EN Esta salida está conectada a los cuatro ánodos en la pantalla de siete segmentos.

player_LED Esta salida es una señal de 2 paquetes que está conectada a los LED encima de los interruptores player1 y player2. El primer jugador en activar su interruptor correspondiente será indicado por el LED. Tenga en cuenta que ambos LED no pueden estar encendidos simultáneamente.

Paso 3: Conexión del altavoz externo

Para conectar el altavoz externo a la placa Basys3, tome sus dos cables y conéctelos como se indica en la imagen de arriba. La línea blanca conecta el terminal negativo del altavoz al puerto de tierra en la placa. La línea roja conecta el terminal positivo del altavoz al puerto pmod JA10 en la placa.

El archivo de restricciones está diseñado para que funcione cualquier puerto de JA1 a JA10. Sin embargo, algunos pines de la placa no responden, por lo que si JA10 no funciona, puede probar los otros puertos.

Paso 4: diagrama estructural

La imagen de arriba muestra el diagrama estructural del sistema de timbre de la competencia que incluye todos los componentes que componen el módulo principal. Sus descripciones son las siguientes:

player_lockout_LED1 El componente LED de bloqueo del reproductor es una máquina de estado finito que usa codificación one-hot. Tiene cuatro entradas: player1, player2, reset y CLK. Contiene un player_LED de salida de paquete de 2 bits. Las entradas y salidas del componente player_lockout_LED1 están todas directamente conectadas a las entradas y salidas del módulo principal con nombres idénticos.

buzzer_tone1 El componente buzzer se basa en este código publicado en un foro

stackoverflow.com/questions/22767256/vhdl-… Sin embargo, se modificó para generar un sonido continuo con una frecuencia de 440 Hz (nota A). La entrada de habilitación está conectada a una señal buzzer_enable que es una salida del componente down_counter_FSM1.

clk_div1 El componente de divisor de reloj es una versión modificada del divisor de reloj del profesor Bryan Mealy que se proporciona en PolyLearn. Ralentiza el reloj por lo que el período de salida es de 1 segundo.

down_counter_FSM1 El contador regresivo es un FSM diseñado para realizar una cuenta regresiva hasta cero. Los dos tiempos de inicio posibles son 20 o 5, que es elegido por la entrada del usuario. Emite '1' cuando el temporizador ha llegado a cero para indicar que se ha agotado el tiempo. Esta salida actúa como una habilitación para el componente de tono del zumbador. El contador también emite una señal de paquete de 8 bits que envía un BCD de 8 bits que se envía al decodificador de segmento. Otra salida es el counter_on que también está conectado a la entrada válida en el decodificador de segmento.

sseg_dec1 El componente decodificador de siete segmentos se proporciona en PolyLearn y fue escrito por el profesor Bryan Mealy. Utiliza una entrada BCD proporcionada por down_counter_FSM1 y genera el equivalente decimal en la pantalla de siete segmentos. Cuando el contador está activado, la entrada válida es alta. Esto permite que el decodificador muestre el número decimal en la pantalla de siete segmentos. Cuando el contador está apagado, la entrada válida es baja. La pantalla de siete segmentos solo mostrará cuatro guiones.

Paso 5: Diagrama de máquina de estados finitos (FSM)

La lista de sensibilidad para la máquina de estados finitos incluye player1, player2, reset y el reloj. La salida FSM es un player_LED de paquete de 2 bits conectado a dos LED en la placa Basys3. La máquina de estados finitos muestra los siguientes tres estados:

ST0 es el estado de inicio. En este estado, los dos LED están apagados. El FSM permanecerá en este estado si tanto el jugador1 como el jugador2 están bajos. Un reinicio asincrónico también establece el estado en ST0. Cuando el interruptor player1 está en alto, el siguiente estado será ST1. Si el interruptor player2 está en alto, el siguiente estado será ST2.

ST1 es el estado en el que el LED player1 está encendido. El FSM permanecerá en este estado para cualquier entrada. Esto significa que incluso cuando el interruptor del jugador2 se establece en alto inmediatamente después de que el interruptor del jugador1 está en alto, permanecerá en ST1. Solo el reinicio asíncrono puede establecer el siguiente estado en ST0.

ST2 es el estado en el que el LED player2 está encendido. Similar a ST !, el FSM permanecerá en este estado para cualquier entrada, incluso cuando el interruptor player1 esté en alto inmediatamente después de que el interruptor player2 esté en alto. Nuevamente, solo el reinicio asíncrono puede establecer el siguiente estado en ST0.

Recomendado:

Nest Hello - Timbre de timbre con transformador integrado Reino Unido (220-240 V CA - 16 V CA): 7 pasos (con imágenes)

Nest Hello - Timbre de timbre con transformador integrado Reino Unido (220-240 V CA - 16 V CA): Quería instalar un timbre Nest Hello en casa, un aparato que funciona con 16 V-24 V CA (NOTA: una actualización de software en 2019 cambió la rango de versión a 12V-24V AC). El timbre estándar suena con transformadores integrados disponibles en el Reino Unido en el

Adaptación de un timbre con video a un timbre de canción digital: 5 pasos

Adaptación de un timbre de video a un timbre de canción digital: Para resumir, Best Buy me dijo que no podía instalar el timbre de puerta Simplisafe con un timbre de puerta con melodía de canción. Al leer cientos de publicaciones, se dijo que no se puede hacer. Simplisafe dijo que no se puede hacer, pero proporcionó un kit de todos modos. El kit de conectores es para un bar st

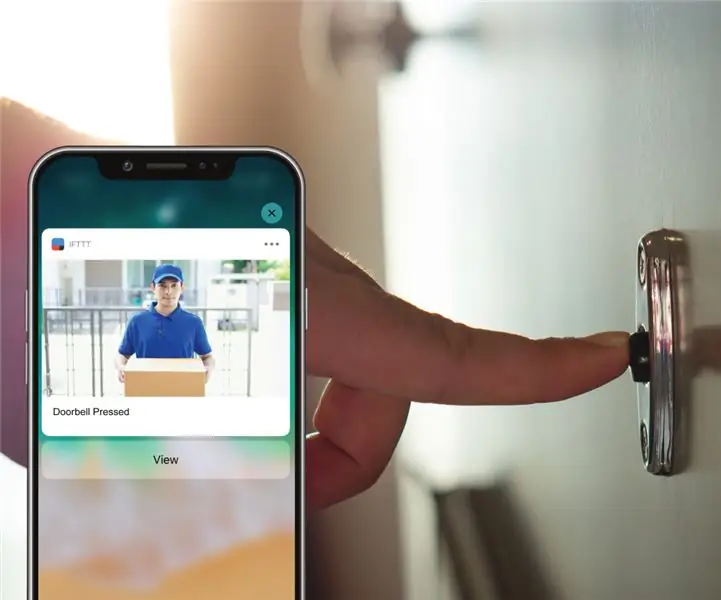

Convierta su timbre con cable en un timbre inteligente con IFTTT: 8 pasos

Convierta su timbre con cable en un timbre inteligente con IFTTT: el timbre WiFi convierte su timbre con cable existente en un timbre inteligente. https://www.fireflyelectronix.com/product/wifidoor

Conexión del timbre con video SimpliSafe a un timbre digital: 6 pasos

Conexión del timbre con video SimpliSafe a un timbre digital: Recientemente compré un timbre con video SimpliSafe y después de instalarlo descubrí que hacía que mi timbre digital sonara constantemente. Después de hablar con SimpliSafe y de que le dijeran que el timbre no está diseñado para funcionar con un timbre digital, ellos

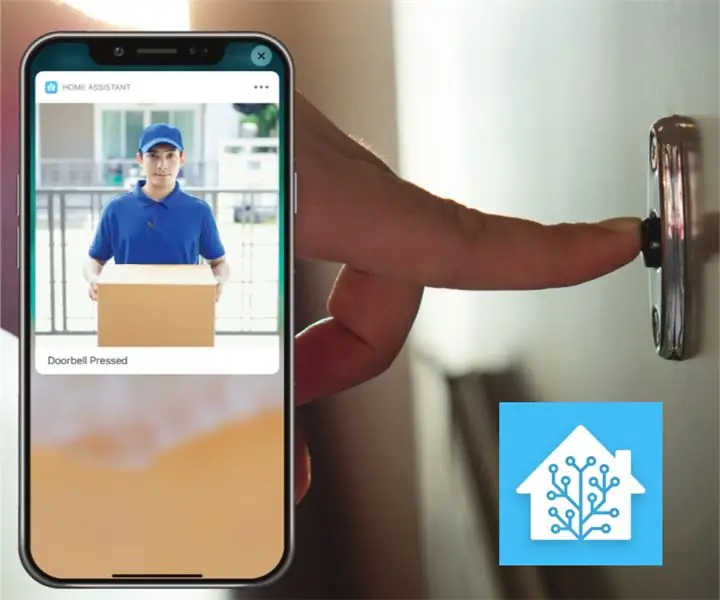

Convierta su timbre con cable en un timbre inteligente con Home Assistant: 6 pasos

Convierta su timbre con cable en un timbre inteligente con Home Assistant: Convierta su timbre con cable existente en un timbre inteligente. Reciba una notificación en su teléfono o conéctese con la cámara de la puerta principal existente para recibir una alerta de foto o video cada vez que alguien toque el timbre. Obtenga más información en: fireflyelectronix.com/pro