Tabla de contenido:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:42.

- Última modificación 2025-01-23 14:39.

Estoy abrumado por el tipo de respuestas que recibo en este blog. Gracias a todos por visitar mi blog y motivarme a compartir mis conocimientos con ustedes. En esta ocasión, voy a presentar el diseño de otro módulo interesante que vemos en todos los SOC: Interrupt Controller.

Diseñaremos un controlador de interrupciones programable simple pero potente. Es un diseño completamente configurable y parametrizado que es portátil entre plataformas. Diseñé esto después de leer mucho sobre algunas arquitecturas populares de controladores de interrupciones como NVIC, 8259a, RISC-V PLIC, INTC de Microblaze, etc. con la ayuda de un controlador de interrupciones.

Paso 1: especificaciones

Las siguientes son las especificaciones de la IP:

- Interfaz AHB3-Lite.

-

Parámetros configurables estáticamente:

- No. de fuentes de interrupción externas; admite hasta 63 interrupciones.

- No. de niveles de prioridad; admite hasta 63 niveles.

- No. de niveles de anidación; admite hasta 8 niveles de anidación.

- Ancho de bus; 32 o 64.

- Interrupciones enmascarables global y localmente.

- Nivel de prioridad configurable dinámicamente para cada interrupción.

- Dos modos de funcionamiento: modo totalmente anidado y modo de igual prioridad.

- Admite interrupciones sensibles activas de alto nivel.

En el diseño se utiliza un mecanismo de protocolo de enlace de interrupción inspirado en las especificaciones RISC-V PLIC.

La preferencia de interrupción está inspirada en 8259a

Otras lecturas: Microblaze INTC, NVIC

Paso 2: descripción general de PIC

El controlador de interrupción programable (PIC) recibe múltiples interrupciones de periféricos externos y las fusiona en una única salida de interrupción a un núcleo de procesador de destino.

El PIC se controla mediante registros de control y estado. Todos los registros PIC están mapeados en memoria y se accede a ellos a través de la interfaz de bus AHB3-Lite.

El banco de registros consta de registro de configuración, registros de habilitación, registros pendientes, registros en servicio, registros de prioridad y registro de ID, que son típicos de los controladores de interrupciones.

El registro de configuración se utiliza para establecer el modo de funcionamiento del PIC. Puede funcionar en modo totalmente anidado o en modo de igual prioridad.

A cada interrupción se le pueden asignar prioridades y enmascarar individualmente. También se admite el enmascaramiento global de todas las interrupciones.

El banco de registros interactúa con Priority Resolver y BTC (Binary-Tree-Comparator) para resolver las prioridades de las interrupciones pendientes y afirmar la interrupción al procesador en consecuencia. El registro de ID contiene el ID de la interrupción pendiente de mayor prioridad.

Paso 3: Diseño e implementación de RTL

El diseño de PIC hace hincapié en reducir la latencia de la resolución de prioridades, que es la parte más crítica en el tiempo del diseño. Dado que el diseño resuelve las prioridades en un solo ciclo de reloj, el rendimiento se degrada con el aumento del número de fuentes con una complejidad Log2.

El diseño se implementó con éxito y se verificó el tiempo hasta las siguientes frecuencias en los FPGA Artix-7.

- Hasta 15 fuentes: 100 MHz

- Hasta 63 fuentes: 50 MHz

La latencia de interrupción agregada solo por PIC es de 3 ciclos de reloj (excluyendo el tiempo de cambio de contexto del procesador y el tiempo de búsqueda de la primera instrucción ISR).

Paso 4: notas importantes y archivos adjuntos

Notas importantes:

- Si no desea la interfaz AHB3-Lite, puede cambiar el módulo superior y utilizar el diseño esquelético de PIC. Sin embargo, el banco de pruebas proporcionado es para IP con interfaz AHB3-Lite.

- PIC IP v1.0 es un diseño RTL desnudo completamente portátil.

- Verificado funcionalmente para trabajar en ambos modos.

Archivos adjuntos:

- Diseño de códigos y banco de pruebas en VHDL.

- Documentación completa de IP.

Es un diseño de código abierto … Siéntete libre de usar …

Para cualquier consulta, en cualquier momento:

Mitu Raj

Recomendado:

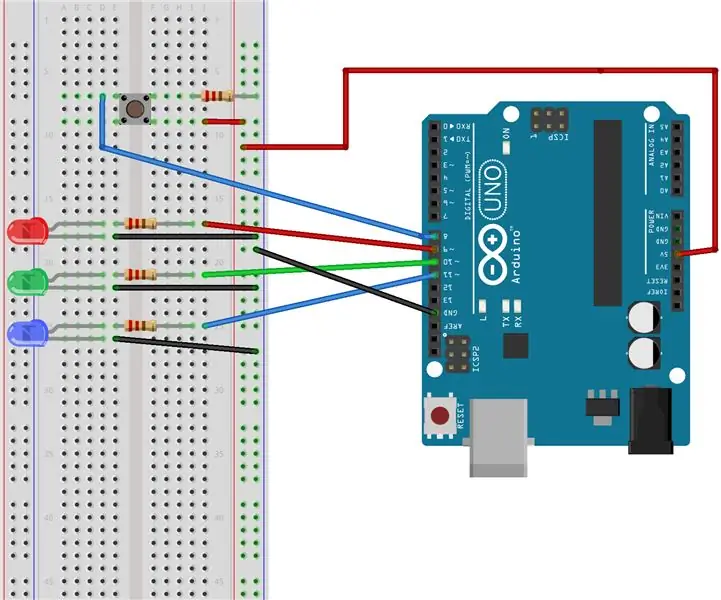

Laboratorio de interrupciones (trabajo en curso): 3 pasos

Laboratorio de interrupciones (trabajo en curso): el propósito de este laboratorio es ejecutar un programa Arduino utilizando interrupciones. Este laboratorio no está funcionando correctamente debido a problemas de codificación Lo que necesitará: - 1 Arduino Uno- 1 Placa de pruebas- 1 botón pulsador- 3 LED's- Resistencias de 220 Ohm- Cables de puente

Diseño de un controlador de caché asociativo de cuatro vías simple en VHDL: 4 pasos

Diseño de un controlador de caché asociativo de conjunto de cuatro vías simple en VHDL: en mi instructable anterior, vimos cómo diseñar un controlador de caché mapeado directo simple. Esta vez, avanzamos un paso. Diseñaremos un controlador de caché asociativo de cuatro vías simple. Ventaja ? Menos tasa de fallos, pero a costa de perfo

Diseño de un controlador de caché simple en VHDL: 4 pasos

Diseño de un controlador de caché simple en VHDL: estoy escribiendo este instructivo, porque me resultó un poco difícil obtener algo de código VHDL de referencia para aprender y comenzar a diseñar un controlador de caché. Así que diseñé un controlador de caché desde cero y lo probé con éxito en FPGA. Tengo p

Diseño de un controlador VGA simple en VHDL y Verilog: 5 pasos

Diseño de un controlador VGA simple en VHDL y Verilog: En este instructable, vamos a diseñar un controlador VGA simple en RTL. El controlador VGA es el circuito digital diseñado para controlar pantallas VGA. Lee de Frame Buffer (memoria VGA) que representa el marco que se mostrará y genera la necesidad

Sensor de efecto Hall Arduino con interrupciones: 4 pasos

Sensor de efecto Hall Arduino con interrupciones: Hola a todos, Hoy les mostraré cómo puede conectar un sensor de efecto Hall a un Arduino y usarlo con una interrupción.Herramientas y materiales utilizados en el video (enlaces de afiliados): Arduino Uno: http : //s.click.aliexpress.com/e/biNyW0zK Sensores de efecto Hall: h