Tabla de contenido:

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:41.

- Última modificación 2025-01-23 14:39.

En este Instructable, describiremos cómo implementar un convertidor de analógico a digital (ADC) de 8 bits en el SLG46855V que puede detectar la corriente de carga y la interfaz con un MCU a través de I2C. Este diseño se puede utilizar para diversas aplicaciones de detección de corriente, como amperímetros, sistemas de detección de fallas y medidores de combustible.

A continuación, describimos los pasos necesarios para comprender cómo se ha programado la solución para crear el sentido de corriente ADC. Sin embargo, si solo desea obtener el resultado de la programación, descargue el software GreenPAK para ver el archivo de diseño GreenPAK ya completado. Conecte el kit de desarrollo GreenPAK a su computadora y presione el programa para crear el sentido de corriente ADC.

Paso 1: Arquitectura ADC

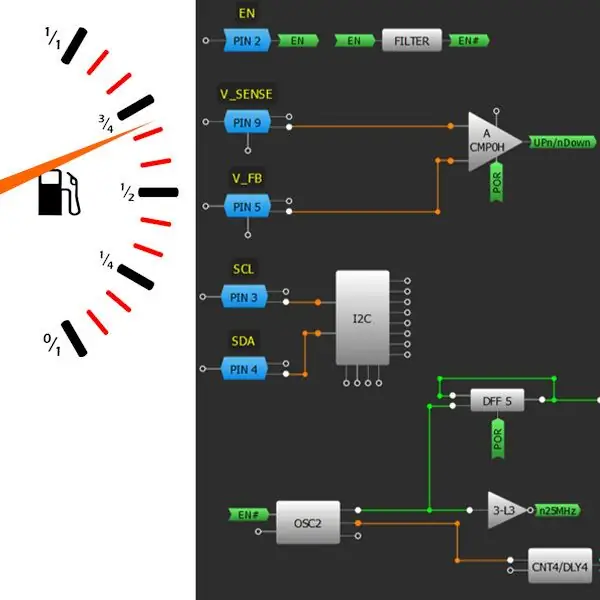

El ADC se compone esencialmente de un comparador analógico y un convertidor de digital a analógico (DAC). El comparador detecta el voltaje de entrada frente al voltaje de salida del DAC y, posteriormente, controla si se incrementa o disminuye el código de entrada del DAC, de modo que la salida del DAC converja al voltaje de entrada. El código de entrada DAC resultante se convierte en el código de salida digital ADC.

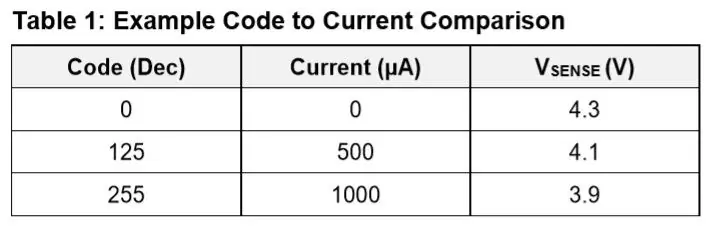

En nuestra implementación, creamos un DAC usando una red de resistencias controlada por modulación de ancho de pulso (PWM). Podemos crear fácilmente una salida PWM precisa controlada digitalmente usando GreenPAK. El PWM cuando se filtra se convierte en nuestro voltaje analógico y, por lo tanto, sirve como un DAC efectivo. Una clara ventaja de este enfoque es que es fácil establecer los voltajes que corresponden al código cero y la escala completa (equivalentemente compensación y ganancia) simplemente ajustando los valores de la resistencia. Por ejemplo, lo ideal es que un usuario lea el código cero de un sensor de temperatura sin corriente (0 µA) correspondiente a 4,3 V, y un código de escala completa a 1000 µA correspondiente a 3,9 V (Tabla 1). Esto se implementa fácilmente simplemente configurando algunos valores de resistencia. Al hacer que el rango del ADC coincida con el rango del sensor de interés, hacemos un mayor uso de la resolución del ADC.

Una consideración de diseño para esta arquitectura es que una frecuencia PWM interna debe ser mucho más rápida que la tasa de actualización del ADC para evitar un comportamiento subamortiguado de su bucle de control. Como mínimo, debería ser más largo que el reloj del contador de datos del ADC dividido por 256. En este diseño, el período de actualización del ADC se establece en 1.3312 ms.

Paso 2: circuito interno

El ADC flexible se basa en el diseño presentado en Dialog Semiconductor AN-1177. La velocidad del reloj se incrementa de 1 MHz a 12,5 MHz para sincronizar el contador ADC ya que el SLG46855 tiene un reloj de 25 MHz disponible. Esto permite una tasa de actualización mucho más rápida para una resolución de muestra más fina. La LUT que marca el reloj de datos del ADC se cambia para que pase a través de la señal de 12,5 MHz cuando el PWM DFF es bajo.

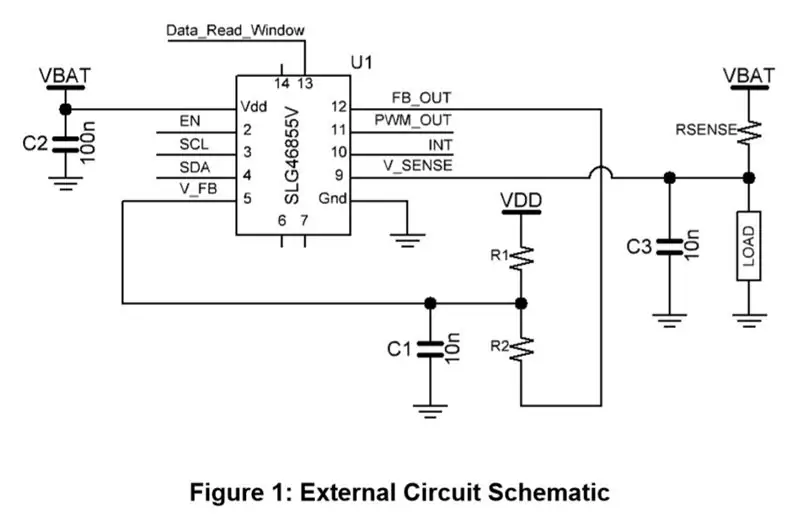

Paso 3: circuito externo

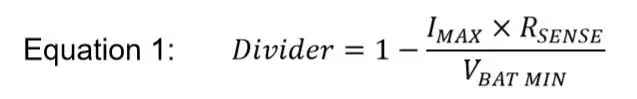

Se utiliza una red de condensadores y resistencias externas para convertir un PWM en un voltaje analógico, como se muestra en el esquema del circuito en la Figura 1. Los valores se calculan para la resolución máxima para la corriente máxima que detectará el dispositivo. Para lograr esta flexibilidad, agregamos las resistencias R1 y R2 en paralelo a VDD y tierra. Un divisor de resistencia divide VBAT al lado bajo del rango de voltaje. La relación del divisor para un VBAT mínimo esperado se puede resolver usando la ecuación 1.

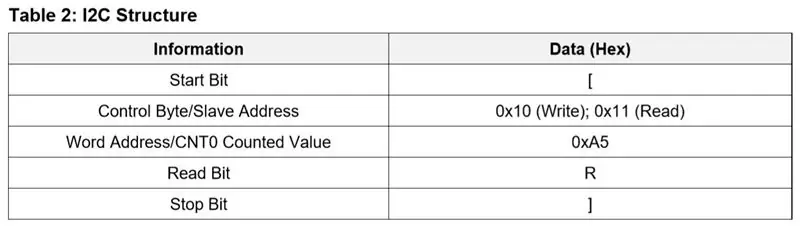

Paso 4: Instrucciones de lectura de I2C

La Tabla 1 describe la estructura del comando I2C para volver a leer los datos almacenados en CNT0. Los comandos I2C requieren un bit de inicio, un byte de control, una dirección de palabra, un bit de lectura y un bit de parada.

A continuación se escribe un comando I2C de ejemplo para volver a leer el valor contado CNT0:

[0x10 0xA5] [0x11 R]

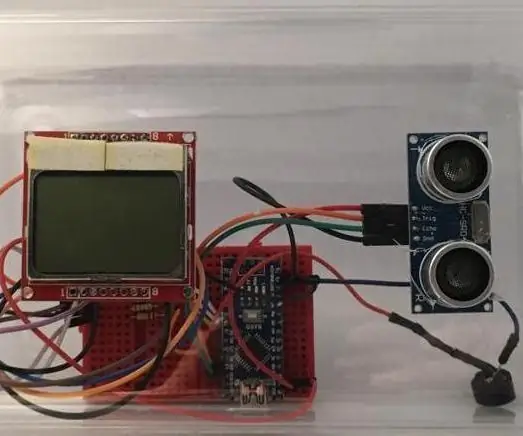

El valor contado que se vuelve a leer será el valor del código ADC. Como ejemplo, se incluye un código Arduino en el archivo ZIP de esta nota de aplicación en el sitio web de Dialog.

Paso 5: resultados

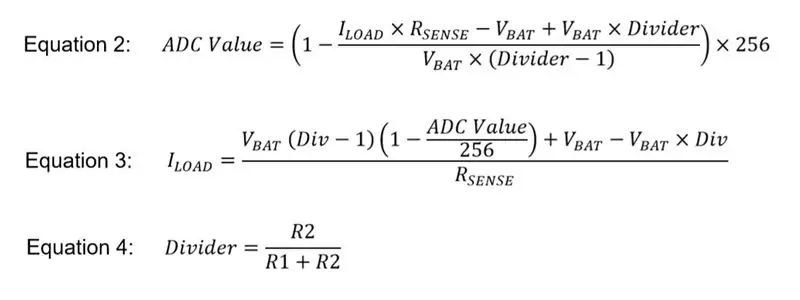

Para probar la precisión del diseño de detección de corriente ADC, los valores medidos a una corriente de carga y un nivel de VDD dados se compararon con un valor teórico. Los valores teóricos de ADC se calcularon con la ecuación 2.

El ILOAD que se correlaciona con un valor de ADC se encuentra con la ecuación 3.

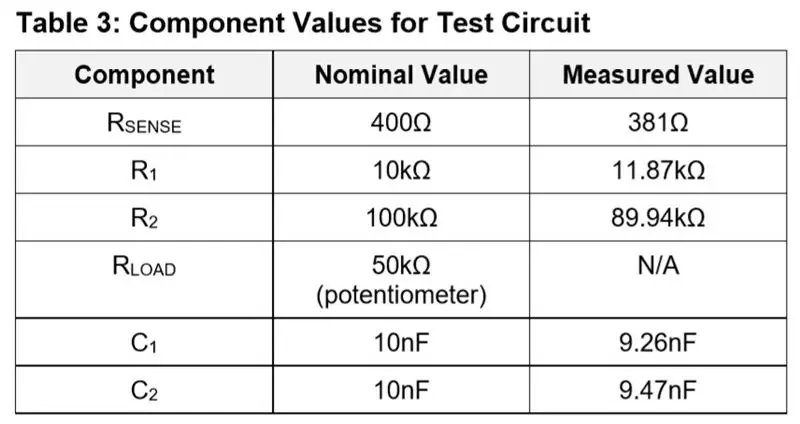

Para los siguientes resultados, utilicé los valores de estos componentes que se muestran en la Tabla 3.

La resolución del valor ADC a la conversión ILOAD se puede calcular usando la ecuación 3 con los valores medidos en la Tabla 2 y el valor ADC establecido en 1. Con un VBAT de 3.9 V, la resolución es 4.96 µA / div.

Para optimizar el circuito de detección de corriente ADC a un nivel VDD mínimo de 3.6 V con una corriente máxima de 1100 µA y una resistencia de detección de 381 Ω, el coeficiente divisor ideal sería 0.884, basado en la ecuación 1. Con los valores dados en la Tabla 2, el divisor real tiene un coeficiente divisor de 0,876. Dado que esto es un poco menor, permitirá un rango de corriente de carga un poco más grande para que los valores de ADC estén cerca del rango completo pero no se desborden. El valor real del divisor se calcula con la ecuación 4.

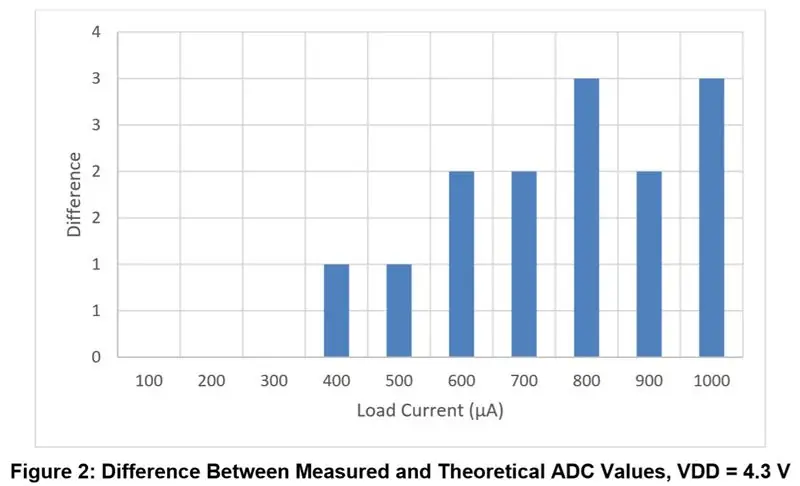

Arriba (Figuras 2-6, Tablas 4-6) están las medidas tomadas del circuito en tres niveles de voltaje: 4.3 V, 3.9 V y 3.6 V. Cada nivel muestra un gráfico que muestra la diferencia entre los valores ADC medidos y teóricos. Los valores teóricos se redondean al entero más cercano. Hay un gráfico de resumen para comparar las diferencias en los tres niveles de voltaje. Posteriormente hay un gráfico que muestra la correlación entre los valores teóricos de ADC y la corriente de carga en los diferentes niveles de voltaje.

Conclusión

El dispositivo fue probado en tres niveles de voltaje: 3.6 V, 3.9 V y 4.3 V. El rango de estos voltajes modela una batería de iones de litio completa que se descarga a su nivel nominal. De los tres niveles de voltaje, se observa que el dispositivo normalmente era más preciso a 3,9 V para el circuito externo elegido. La diferencia entre los valores ADC medidos y teóricos fue de solo 1 valor decimal con corrientes de carga de 700 - 1000 µA. En el rango de voltaje dado, los valores de ADC medidos fueron 3 puntos decimales por encima de las condiciones nominales en el peor de los casos. Se pueden realizar más ajustes al divisor de resistencia para optimizar diferentes niveles de voltaje VDD.

Recomendado:

Cómo hacer que un temporizador tenga menos contacto para lavarse las manos # Covid-19: 3 pasos

Cómo hacer que un temporizador tenga menos contacto para lavarse las manos # Covid-19: ¡Hola! Este tutorial le mostrará cómo hacer que un temporizador tenga menos contacto. de hecho, en este período de epidemia de coronavirus, es muy importante lavarse bien las manos. Es por eso que he creado este temporizador. Para este temporizador he utilizado una pantalla LCD Nokia 5110

Desmontaje del letrero solar del anillo: lo hice mal para que usted no tenga que hacerlo: 11 pasos

Ring Solar Sign Teardown: Lo hice mal para que no tengas que hacerlo: Tengo un Ring Doorbell, que es bastante impresionante. Yay por Ring. Luego obtuve una cámara Ring Stick-up cuando todas las ventas en línea alrededor del Día de Acción de Gracias estaban en marcha. $ 50 de descuento, y me enviaron este ingenioso letrero solar de Ring GRATIS (¡solo por un valor de $ 49!). Estoy seguro de que

Luz reactiva a la música -- Cómo hacer una luz reactiva a la música súper simple para hacer que el escritorio sea impresionante: 5 pasos (con imágenes)

Luz reactiva de música || Cómo hacer luz reactiva de música súper simple para hacer un escritorio impresionante: Hola chicos, hoy construiremos un proyecto muy interesante. Hoy vamos a construir luz de música reactiva. el bajo, que en realidad es una señal de audio de baja frecuencia. Es muy simple de construir. Nosotros

Cómo hacer una rana zumbadora, la cosa más aleatoria y sin sentido --- ¡¡NUNCA !!: 6 pasos

Cómo hacer una rana zumbante, la cosa más aleatoria y sin sentido --- ¡¡NUNCA !!: Bueno, un día estaba aburrido, así que decidí hacer algunas cosas divertidas. Aquí hay una rana zumbante, y en la parte de atrás habrá una interruptor basculante (o cualquier interruptor, su elección) y cuando lo encienda, la rana zumbará. ¡Artículo genial y muy poco! Rango de precios de

Hacer que su editor de Visual Studio tenga un fondo de color: 3 pasos

Hacer que su editor de Visual Studio tenga un fondo de color: cambie el color de fondo de su editor de código para que pueda ver mejor, poner menos esfuerzo en sus ojos o enfocar mejor