Tabla de contenido:

- Paso 1: Operación del secuenciador digital por parte del usuario

- Paso 2: Detalles técnicos

- Paso 3: Detalles técnicos

- Paso 4: Divisor de reloj de 7 segmentos

- Paso 5: Divisor del reloj de pulsaciones por minuto

- Paso 6: Divisor del reloj de tonos

- Paso 7: Reproducir / Pausar / Seleccionar máquina de estado

- Paso 8: Reproducir / Pausar / Seleccionar máquina de estado

- Paso 9: Salida FSM

- Paso 10: Salida FSM

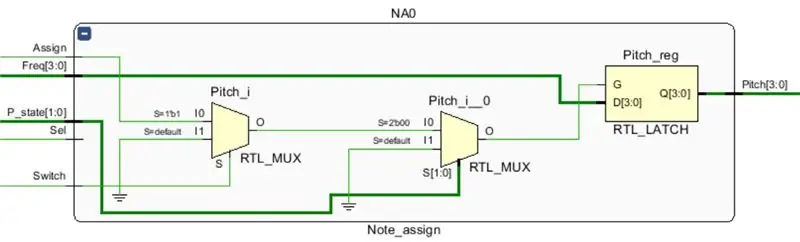

- Paso 11: Asignar nota

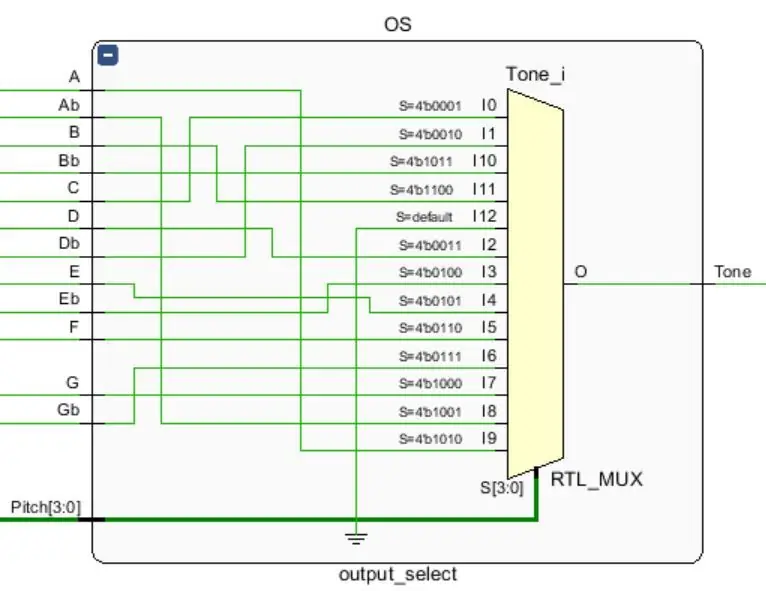

- Paso 12: Selección de salida

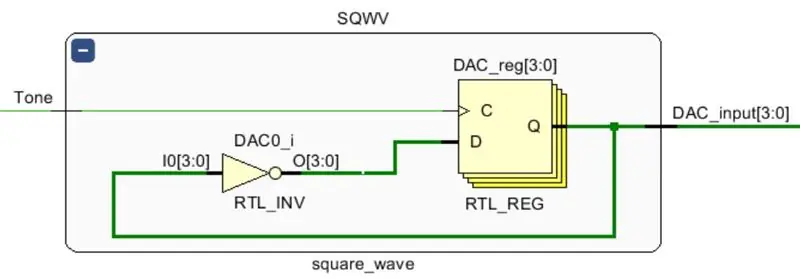

- Paso 13: Generación de onda cuadrada

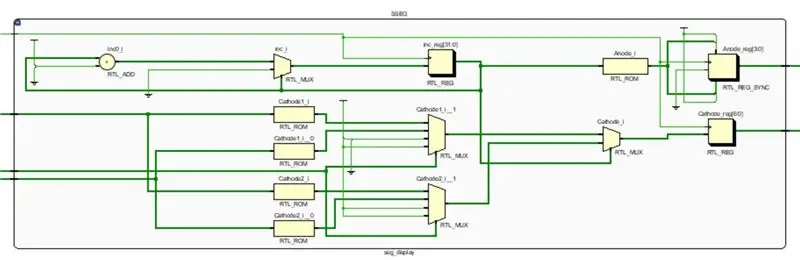

- Paso 14: pantalla de 7 segmentos

- Paso 15: Selección final

- Paso 16: Dispositivos externos: DAC

- Paso 17: Dispositivos externos: altavoz

- Paso 18: demostración de video

- Paso 19: Código VHDL

- Autor John Day day@howwhatproduce.com.

- Public 2024-01-30 08:44.

- Última modificación 2025-01-23 14:40.

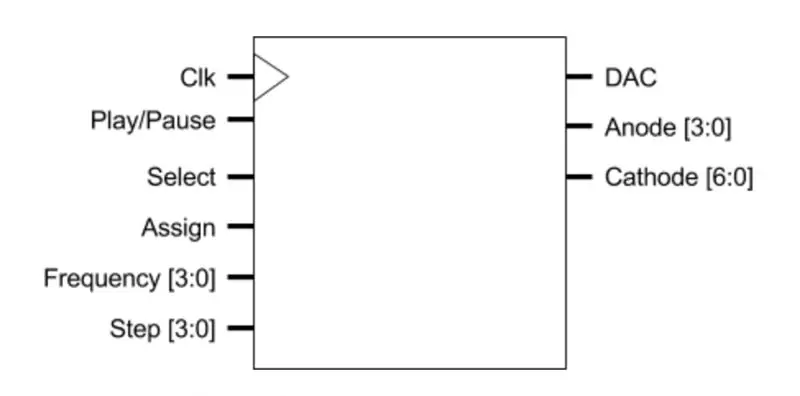

CPE 133, Cal Poly San Luis Obispo

Creadores del proyecto: Jayson Johnston y Bjorn Nelson

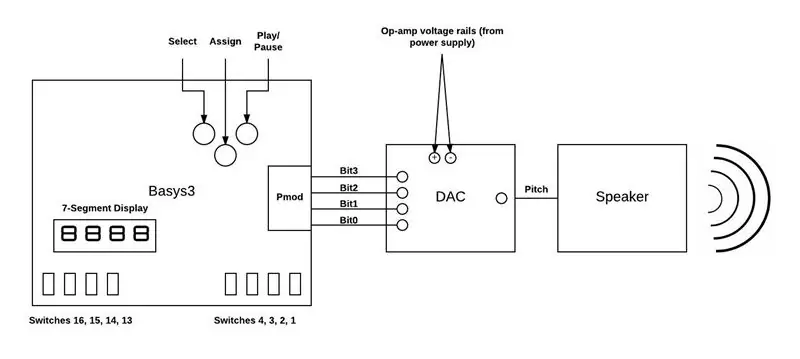

En la industria musical actual, uno de los "instrumentos" más utilizados es el sintetizador digital. Todos los géneros de música, desde hip-hop hasta pop e incluso country, utilizan un sintetizador digital en el estudio para crear los ritmos y sonidos que necesitan para dar vida a su música. En este tutorial, crearemos un sintetizador muy simple con la placa FPGA Basys 3.

El sintetizador podrá tocar cuatro negras seleccionadas a un número constante de tiempos por minuto. Los usuarios utilizarán los interruptores para asignar cada nota negra a un tono musical. Para este proyecto estamos usando un convertidor de digital a analógico (DAC) de 4 bits para tomar la salida de la placa y convertirla en una señal analógica. La salida del DAC luego se enviará a un altavoz de computadora estándar, creando nuestra música. Son posibles dieciséis tonos discretos. Restringiremos nuestro sintetizador a una sola octava de 12 notas, que caen entre C medio (261,6 Hz) y B4 (493,9 Hz). El usuario también tendrá la opción de asignar varias notas al mismo tiempo, así como de asignar un silencio presionando asignar sin que ninguno de los interruptores de tono se mueva hacia arriba. A medida que se selecciona y se reproduce cada nota, la nota de la letra se muestra en la pantalla de 7 segmentos. También usaremos tres de los botones del tablero, uno para reproducir y pausar la música, uno para reiniciar el sintetizador y ponerlo en modo de “selección”, y el tercero para asignar un tono a cada nota mientras está en modo de selección.

Una vez que el usuario está satisfecho con su elección de notas, y después de presionar el botón de reproducción, el sintetizador reproducirá cada nota en sucesión repetidamente hasta que el usuario presione pausa o seleccione.

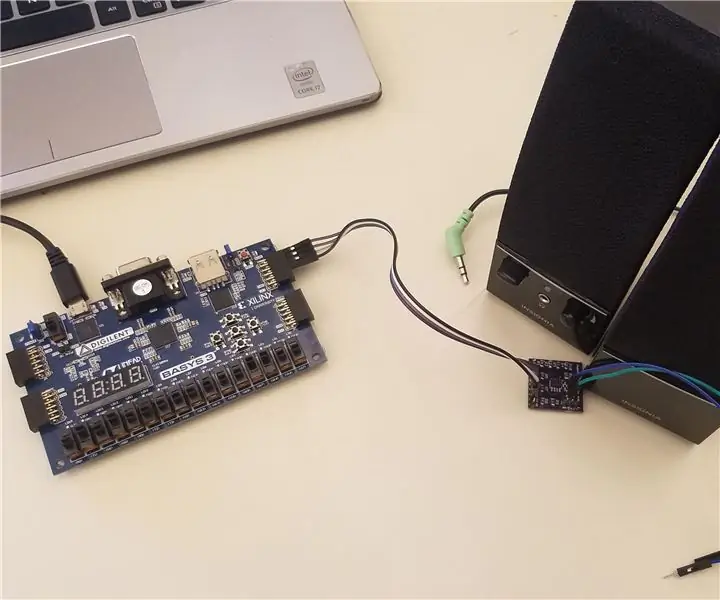

Aquí hay una lista del equipo requerido:

- Vivado (o cualquier espacio de trabajo VHDL)

- Placa FPGA Basys 3 o similar

- Convertidor digital a analógico (mínimo 4 bits)

- Altavoz con conector para auriculares

- Conductores de alambre

Paso 1: Operación del secuenciador digital por parte del usuario

Los siguientes pasos son para operar el secuenciador digital. El secuenciador digital admite la reproducción de 12 tonos distintos (C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B), que van desde 261,6 Hz a 493,9 Hz.

1. Presione el botón izquierdo para poner el tablero en modo de selección. Cuando esté en este modo, los 4 interruptores más a la izquierda (interruptores 13 a 16) se usarán cada uno para almacenar un valor de tono distinto.

2. Para hacer una selección, encienda uno de los interruptores de la izquierda y luego use los 4 interruptores de la derecha (interruptores 1 a 4) para elegir el tono deseado. El tono asociado con una combinación específica de interruptores derechos se mostrará en la pantalla de siete segmentos, y la pantalla se actualizará al nuevo tono asociado cada vez que los interruptores derechos se cambien a una nueva combinación. Se puede asignar un silencio no asignando nunca un tono a uno de los interruptores de la izquierda, o asignando un tono mostrado como 0 en la pantalla a la nota. Una vez que se ha encontrado el tono deseado y se muestra en la pantalla, presione el botón de asignación inferior para asignar ese tono específico a la nota.

3. Repita el paso 2 para las tres notas restantes, activando cada uno de los interruptores izquierdos restantes individualmente, eligiendo el tono respectivo con los interruptores derechos y presionando el botón inferior para asignar el tono a la nota. Se puede asignar el mismo tono a varias notas cambiando más de uno de los interruptores de la izquierda hacia arriba al mismo tiempo.

4. Ahora que se han asignado todos los tonos de nota, el secuenciador digital está listo para tocar. Para reproducir las notas en el altavoz, simplemente presione el botón derecho de reproducción / pausa para comenzar a reproducir la música. El orden de la secuencia de reproducción refleja los tonos asociados con los interruptores izquierdos, de izquierda a derecha. Las notas se tocarán a un número determinado de tiempos por minuto, en el orden 1, 2, 3, 4, 1, 2…. La pantalla mostrará la nota que se está reproduciendo actualmente mientras los altavoces reproducen la música. Para pausar la reproducción de música, simplemente presione el botón derecho, y luego la música dejará de reproducirse y se mostrará un símbolo de pausa en la pantalla. Si vuelve a pulsar el botón derecho, se reanudará la reproducción.

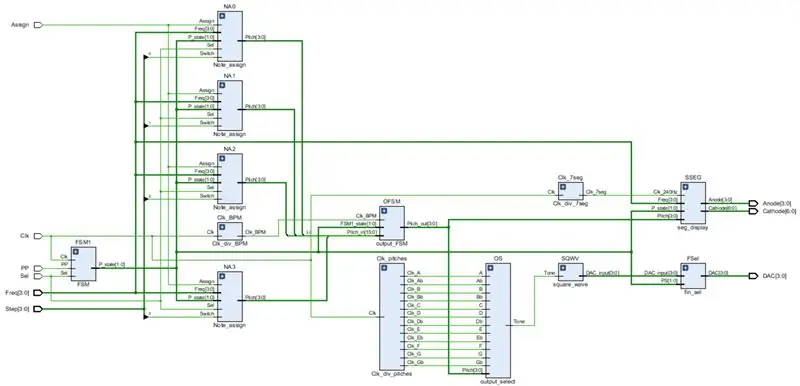

Paso 2: Detalles técnicos

Nuestro sintetizador utiliza muchos componentes digitales diferentes. Se incluyen máquinas de estados finitos, registros, multiplexores, divisores de reloj y más. Para construir nuestro sintetizador, usamos 10 archivos modulares únicos. En lugar de convertir cada módulo en un componente, desglosamos los archivos modulares por función. La mayoría de los módulos, como resultado, son más de un componente. Tenga en cuenta que la imagen de arriba muestra todos los bloques unidos en nuestro diseño superior.

Discutiremos cada módulo describiendo las entradas y salidas, desglosando sus componentes y explicando su propósito en el diseño general. Se incluye un archivo ZIP en la parte inferior del instructable, que contiene todos los archivos de código VHDL utilizados en el proyecto.

Entradas

- Clk (señal de reloj nativa)

- PP (reproducir / pausar)

- Sel (poner el sintetizador en modo de selección)

- Asignar (asignar un paso a un tono)

- Paso (las notas posicionales)

- Freq (los interruptores que crean el tono deseado)

Salidas

- Ánodo (ánodos de 7 segmentos)

- Cátodo (cátodos de 7 segmentos)

- DAC (4 bits que controlan el DAC)

Paso 3: Detalles técnicos

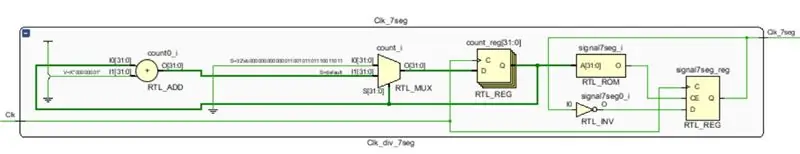

Paso 4: Divisor de reloj de 7 segmentos

Nuestro sintetizador utiliza tres divisores de reloj, todos produciendo señales que tienen un propósito diferente en nuestro proyecto. Un divisor de reloj toma una señal de reloj nativa y produce una señal alterada que tiene una frecuencia menor que la señal de reloj original. El reloj nativo de Basys 3 es de 100 MHz. Esta es la frecuencia que utilizan nuestros divisores de reloj. Si está utilizando una placa FPGA diferente con una frecuencia de reloj nativa diferente, es posible que deba modificar el código.

El divisor de reloj de 7 segmentos produce una señal que impulsa el archivo seg_display. Explicaremos cómo funciona este archivo con más detalle cuando lleguemos a su sección. Básicamente, este divisor de reloj produce una señal de 240 Hz que se utilizará para cambiar entre ánodos y cátodos en la pantalla. La señal es de 240 Hz porque la frecuencia a la que el ojo humano no puede reconocer la ausencia de luz es de 60 Hz. Estamos usando dos dígitos, por lo que al duplicar esta frecuencia, cada dígito oscilará a 60 Hz. Luego lo duplicamos para obtener 240 Hz porque el sistema solo cambia cuando la señal sube, no cuando baja.

Para lograr esto, el divisor toma la señal nativa de 100 MHz y cuenta cada flanco ascendente. Cuando el contador llega a 416667, la salida pasará de menor a mayor, o viceversa.

Entradas

Clk (señal de reloj nativa)

Salidas

Clk_7seg (para seg_display)

Componentes

- D registro

- MUX

- Inversor

- Sumador

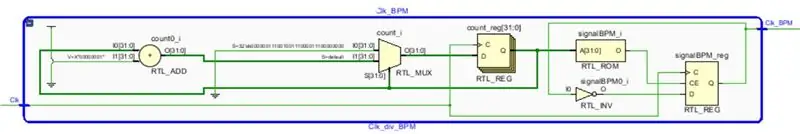

Paso 5: Divisor del reloj de pulsaciones por minuto

El divisor de reloj BPM funciona de manera similar. Este divisor produce la frecuencia de reloj que impulsa la conmutación entre los cuatro pasos cuando se emiten tonos en el estado de reproducción. Decidimos cambiar entre notas a 100 BPM. A 100 BPM, cada nota se reproducirá durante 3/5 de segundo. La señal resultante tendría una frecuencia de 1,67 Hz.

Para producir una señal de esta frecuencia, usamos nuevamente un sistema de conteo, pero esta vez el conteo fue de 60 millones. Cada vez que el contador alcanzaba los 60 millones, la señal de salida cambiaba entre alta y baja.

Entradas

Clk (frecuencia de reloj nativa)

Salidas

Clk_BPM (a salida_FSM)

Componentes

- D registro

- MUX

- Inversor

- Sumador

Paso 6: Divisor del reloj de tonos

El divisor de reloj de tonos es el más grande de nuestros divisores de reloj. Este divisor emite 12 señales diferentes correspondientes a las 12 notas diferentes que nuestro sintetizador puede tocar. Utilizando conocimientos básicos de teoría musical, dedujimos que un bit o bus podría oscilar a una velocidad que corresponde a la frecuencia de las notas musicales. Para ver las frecuencias que usamos, mira aquí. Usamos la cuarta octava de tonos.

Aquí se utiliza el mismo sistema de recuento. Para conocer los valores específicos con los que contamos, consulte el archivo con la etiqueta Clk_div_pitches.

Entradas

Clk (frecuencia de reloj nativa)

Salidas

C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (para seleccionar_salida)

Componentes

- D registro

- MUX

- Inversor

- Sumador

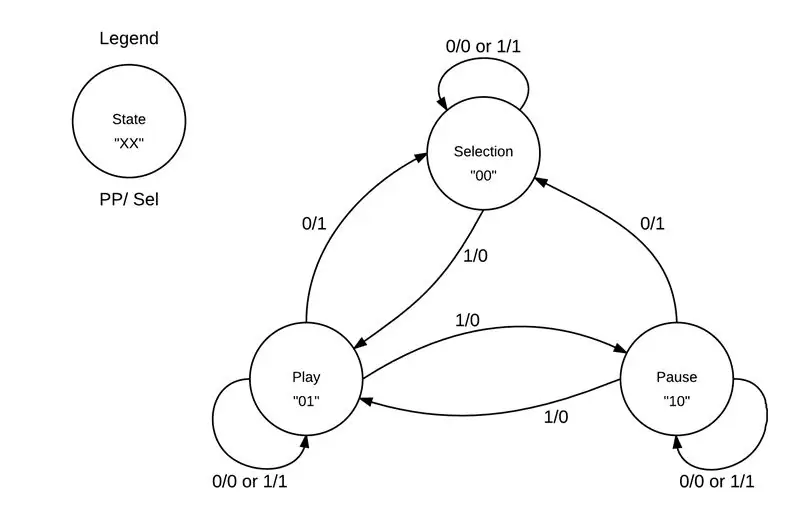

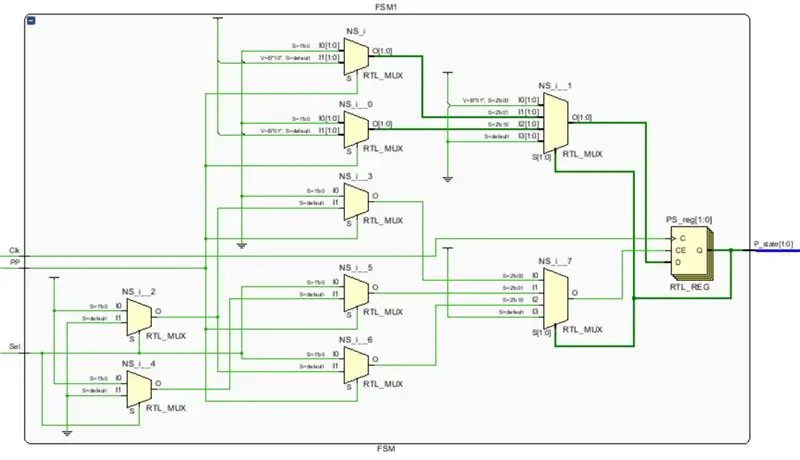

Paso 7: Reproducir / Pausar / Seleccionar máquina de estado

En nuestro proyecto hay dos máquinas de estados finitos (FSM). Un FSM es un dispositivo lógico que puede existir en un solo estado entre una cantidad finita de estados. Usando un FSM, un circuito digital puede moverse a un nuevo estado basado en una combinación de entradas. Usando la lógica de entrada, el estado de un FSM cambiará cuando haya un flanco ascendente del reloj. Desde el estado y las entradas al circuito, puede crear una lógica de salida que proporcione salidas que solo existen si el FSM se encuentra en un estado determinado.

La máquina de estado PPS es la primera FSM en nuestro circuito. Hay tres estados en este FSM; Modo de reproducción, pausa y selección. Para movernos por los diferentes estados, usamos los botones PP y Selección. Consulte el diagrama de estado anterior para ver cómo ocurren las transiciones entre estados. Hicimos esta transición de FSM en el borde ascendente del reloj nativo de 100 MHz, por lo que sería imposible que la máquina no hiciera la transición cuando se presionó uno de los botones, incluso durante un período de tiempo muy corto. El estado actual (P_state) es la única salida de este módulo.

Entradas

- Clk (frecuencia de reloj nativa)

- Sel (botón izquierdo)

- PP (botón derecho)

Salidas

P_state (estado actual, a output_FSM, note_assign, seg_dsiplay, final_select)

Componentes

- MUX

- D registro

Paso 8: Reproducir / Pausar / Seleccionar máquina de estado

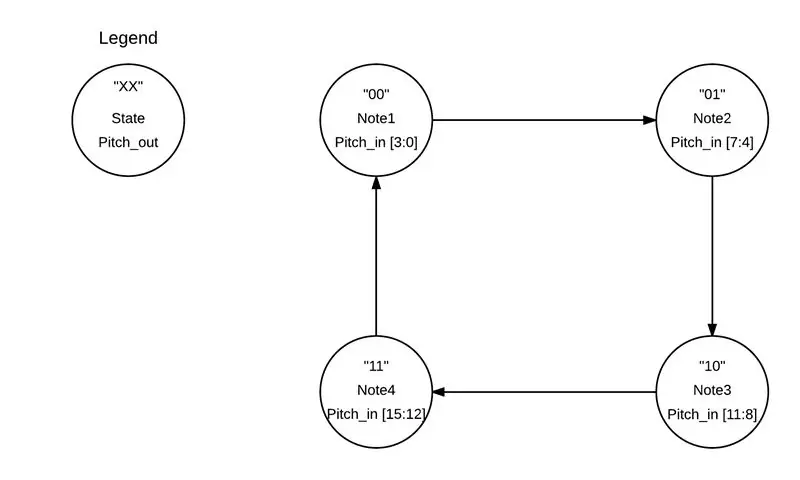

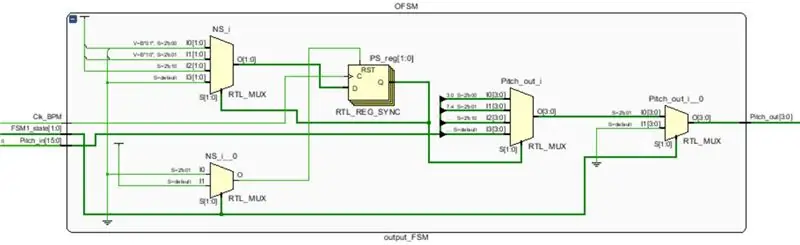

Paso 9: Salida FSM

Este es el segundo FSM al que se hace referencia en la sección anterior. Este FSM tiene una función diferente a la del otro, pero la base de este es esencialmente la misma.

El FSM de salida solo funciona si el estado actual del primer FSM es "01" (el estado de reproducción). Básicamente, esta es la habilitación del módulo. Si el estado es "01", entonces el FSM cambiará entre estados en el borde ascendente de la señal de reloj BPM. Hacemos esto porque output_FSM está controlando qué número binario para el tono seleccionado se envía a los módulos output_select y seg_display. El FSM tiene una entrada de 16 bits que proviene del módulo de asignación de notas, que se tratará a continuación. En el estado "00" para output_FSM, el módulo generará "xxxx" para la primera nota asignada. Luego, en "01", emitirá "yyyy" para la segunda nota y así sucesivamente para cada nota antes de volver a la primera nota. Consulte el diagrama de estado anterior.

Este FSM se diferencia del primero porque no hay una lógica de entrada para controlar la conmutación entre estados. En cambio, el FSM solo funcionará cuando el estado del primer FSM sea "01", y luego este FSM hará la transición entre estados solo en el borde ascendente de la señal de reloj. Otra diferencia es que este módulo tiene lógica de salida, lo que significa que no genera el estado actual, sino que genera el número binario para el tono en ese estado.

Entradas

- Clk_BPM (señal de reloj BPM del divisor de reloj)

- FSM1_state (PS de PPS FSM)

- Pitch_in (tonos de note_assign)

Salidas

Pitch_out (un tono a la vez, para output_select y seg_display)

Componentes

- MUX

- D registro

Paso 10: Salida FSM

Paso 11: Asignar nota

El módulo de asignación de notas es responsable de asignar realmente un tono a la nota posicional o paso. Este módulo es bastante simple. Primero verifica si el circuito está en el estado de "selección" y si un interruptor de paso (extremo izquierdo) está alto. Si esto es cierto y se presiona el botón de asignación, la salida del módulo será igual al número binario representado por los interruptores de frecuencia (extremo derecho).

Originalmente, habíamos intentado hacer un módulo que realmente guardara una de las señales del reloj de tono en la salida, pero experimentamos problemas con el cambio de salida para seguir las señales del reloj de entrada. Este es el único módulo utilizado más de una vez en el diseño final. Cada paso tiene un módulo note_assign asociado, y debido a eso, cada instancia del módulo obtiene un bit del bus Step.

Entradas

- P_state (estado actual de PPS FSM)

- Sel (botón izquierdo)

- Interruptor (interruptor de un paso)

- Freq (interruptores del extremo derecho para el tono)

- Asignar (botón inferior, asigna una nota)

Salidas

Paso (número binario, a output_FSM)

Componentes

- MUX

- D resgistrar

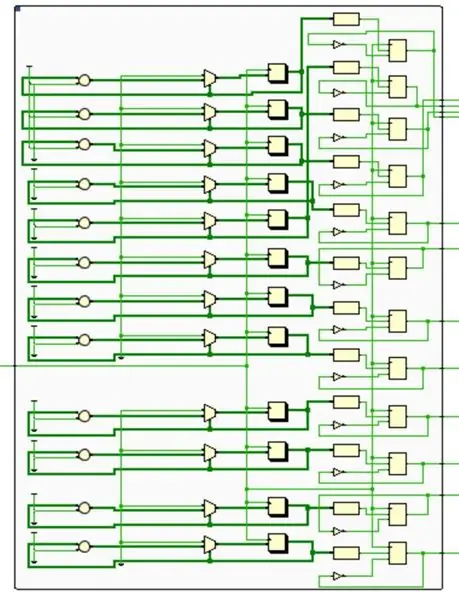

Paso 12: Selección de salida

La selección de salida es responsable de tomar el número binario de un tono y conectarlo a su respectiva señal de reloj. A pesar de su tamaño, este también es un módulo relativamente simple. Output_select es esencialmente un decodificador binario, que decodifica el número binario de un tono a una señal de reloj específica. En realidad, la asignación de la salida a una frecuencia de reloj funcionó mejor aquí en comparación con el módulo note_assign, porque todo lo que este módulo tenía que hacer era MUX las señales de reloj con el número binario que representa la entrada de control.

Nos disculpamos por el extraño enrutamiento, Vivado organizó las señales de tono alfabéticamente para el archivo clk_div_pitches, pero para este archivo las organizó por número binario ascendente, lo que provocó que los tonos estuvieran en un orden diferente. También tenga en cuenta que si el número binario de output_FSM era "0000" o algo mayor que "1100", entonces el MUX se envía a través de una señal '0' plana.

Aporte

- Pitch (de output_FSM);

- C, Db, D, Eb, E, F, Gb, G, Ab, A, Bb, B (señales de reloj de tono)

Producción

Tono (un solo bit que coincide con la señal de reloj seleccionada, a square_wave)

Componentes

MUX

Paso 13: Generación de onda cuadrada

El módulo square_wave es el generador de la onda cuadrada que se emite desde la placa al DAC. Usando la señal de tono del archivo anterior, esta onda cuadrada invierte el número de 4 bits entre "0000" y "1111" en el borde ascendente del tono. El tono es una frecuencia de tono específica, por lo que square_wave produce una onda con una frecuencia diferente cuando output_FSM pasa a otro estado. La salida de 4 bits de este módulo va al módulo fin_sel, donde la lógica dicta si este bus se emitirá según el estado de PPS FSM.

Una alternativa a este generador de ondas cuadradas es producir una onda sinusoidal. Si bien esto probablemente produciría un mejor tono final, es considerablemente más difícil de implementar, por lo que optamos por generar solo una onda cuadrada.

Entradas

Tono (bit oscilante de output_select)

Salidas

DAC_input (bus oscilante de 4 bits que cambia a la misma frecuencia de tono)

Componentes

- Inversor

- D registro

Paso 14: pantalla de 7 segmentos

El módulo seg_display controla la pantalla de 7 segmentos en nuestra placa basys. Dentro del módulo, ocurren dos procesos. El primer proceso decodifica Freq cuando está en el estado de "selección" o Pitch cuando está en el modo de "reproducción". En el modo "pausa", el módulo se decodifica para mostrar el símbolo de pausa. Al observar el código VHDL, puede ver que el decodificador binario realmente decodifica la entrada en dos señales diferentes, cátodo1 y cátodo2. El cátodo1 representa la letra correspondiente al tono que se mostrará y el cátodo2 representa el símbolo plano (b) si lo hay. La razón de esto se relaciona con el segundo proceso realizado por el módulo seg_display.

En una placa basys3, la pantalla de segmento tiene cátodos comunes. Mientras que los ánodos controlan qué dígito está activado, los cátodos controlan qué segmentos están activados. Dado que la pantalla tiene cátodos comunes, eso significa que solo puede mostrar un conjunto de segmentos a la vez. Eso plantea un problema para este proyecto porque queremos mostrar una letra en el primer dígito y el símbolo plano, si es necesario, al mismo tiempo. ¿Ahora recuerdas la señal del reloj de 7 segundos? Para solucionar este problema, cambiamos los ánodos y cátodos hacia adelante y hacia atrás en la señal del reloj de 7 segundos. Debido a que la señal del reloj es de 240 Hz y estamos usando dos dígitos, cada dígito oscilará a 60 Hz. Para el ojo humano, parecerá que los dígitos no oscilan en absoluto.

También tenga en cuenta que la pantalla de la placa basys3 utiliza lógica negativa. Esto significa que si un ánodo o cátodo se establece en '0', ese dígito o segmento estará activado y viceversa.

Entradas

- Tono (número binario de una nota, utilizado en el estado de reproducción)

- Freq (interruptores de frecuencia, usados cuando está en estado de selección)

- P_state (estado actual de PPS FSM)

- Clk_240Hz (señal de reloj de Clk_div_7seg, doble 120 porque solo estamos usando el borde ascendente)

Salidas

- Cátodo (bus que controla segmentos en la pantalla, salida final)

- Ánodo (bus que controla los dígitos en la pantalla, salida final)

Componentes

- Pestillo

- MUX

- D registro

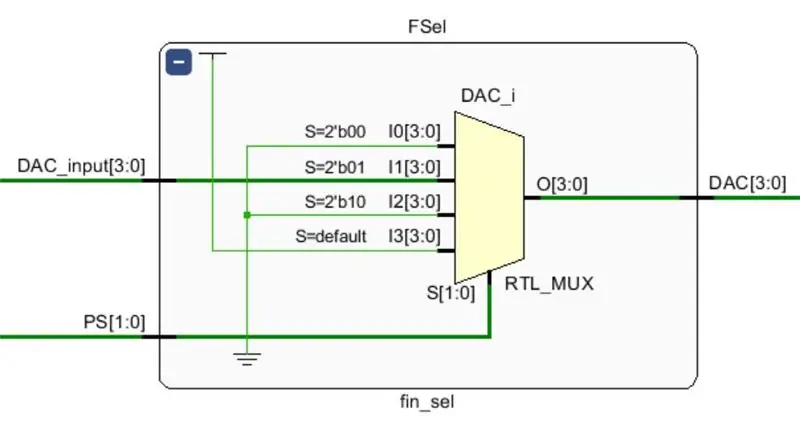

Paso 15: Selección final

La selección final es el último módulo utilizado en este proyecto. Otro módulo simple, este módulo controla la salida final que irá al DAC. Cuando esté en el estado de "selección" o "pausa", el módulo emitirá un "0000" estático para que no se reproduzca música desde los altavoces. En el estado de "reproducción", el módulo emitirá los 4 bits oscilantes según lo determinado por square_wave.

Entradas

- P_state (estado actual de PPS FSM)

- DAC_input (los 4 bits oscilantes de square_wave)

Salidas

DAC (es igual a DAC_input en estado de reproducción, salida final)

Componentes

MUX

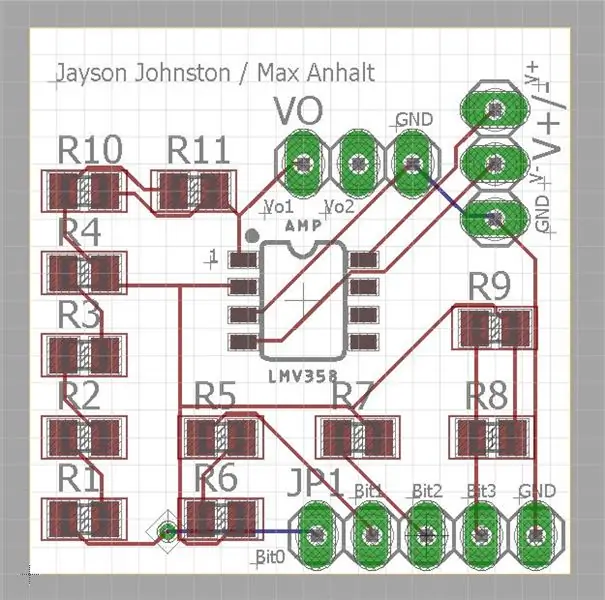

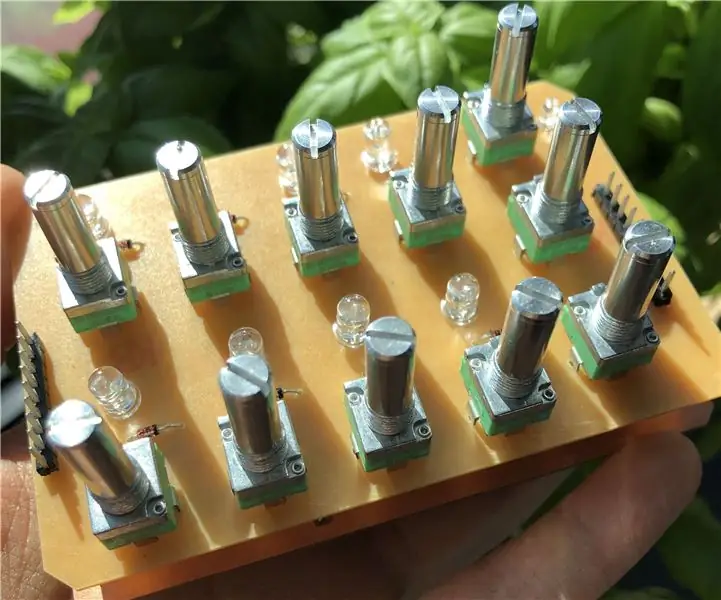

Paso 16: Dispositivos externos: DAC

Un convertidor de digital a analógico (DAC) toma una señal discreta y la convierte en una señal continua. Nuestro DAC tiene cuatro bits y está hecho de un amplificador sumador. Mediante el uso de una relación de resistencias en el bucle de suministro y retroalimentación, pudimos crear un sistema que genera en 16 niveles diferentes mediante la "suma" de cada rama. Bit0, la rama superior, tiene el menor peso y aporta el menor potencial cuando está alta debido a que las ramas tienen una mayor resistencia. El peso aumenta a medida que bajas por las ramas. Si tuviera que contar en binario hacia arriba y luego hacia abajo usando las entradas de bit, los voltajes de salida se verían como una onda sinusoidal escalonada. La entrada al DAC se conectó a uno de los PMOD en la placa para transferir la señal de 4 bits.

El DAC se ensambló originalmente para una clase de Ingeniería Eléctrica y fue diseñado y soldado por nosotros, no comprado en una tienda. Arriba hay una imagen del archivo de diseño para crear la placa de circuito impreso.

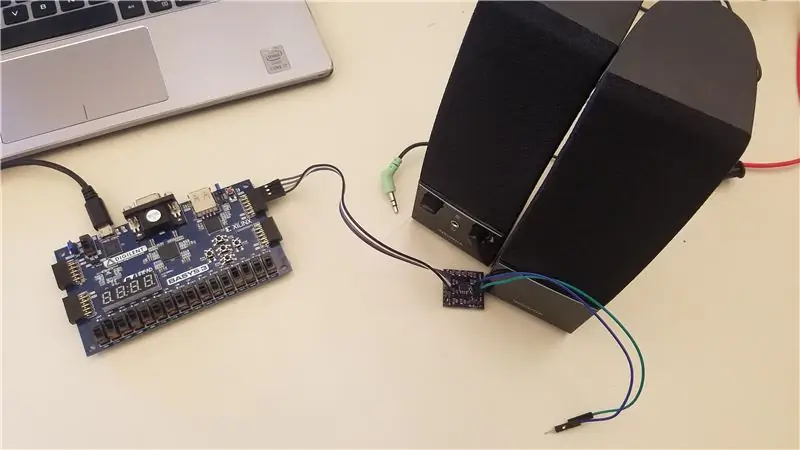

Paso 17: Dispositivos externos: altavoz

Para este proyecto, no querrás comprar un par de parlantes súper bonitos. Como puede ver, el sonido es bastante básico. Fuimos y compramos un juego de parlantes para computadora de $ 8 de Best Buy. Todo lo que tenga un conector para auriculares funciona bien. Monotone también funciona bien. Incluso puedes usar auriculares, ¡pero podrías apagarlos!

Para conectar la salida del DAC a los altavoces, usamos cables de puente y luego sujetamos el cable de salida a la punta del conector de auriculares y el cable de tierra a la base. Intentamos usar cinta aislante para mantener los cables en su lugar, pero causó mucha interferencia. Probar con un estilo diferente de cinta podría resolver este problema.

Para nuestros altavoces, los ajustamos al ajuste más alto y obtuvimos un ruido bastante alto.

¡Y ese es el último paso para crear un secuenciador digital a partir de una placa FPGA! Vaya a las siguientes dos secciones para descargar todo nuestro código VHDL y ver el secuenciador en acción.

Paso 18: demostración de video

Este video muestra la versión final del proyecto de trabajo, incluido el proceso de asignación de los interruptores a 4 tonos distintos y los altavoces que tocan las notas respectivas.

Paso 19: Código VHDL

Aquí está el código para todo el proyecto, incluidos los archivos de restricción y sim utilizados durante la construcción del secuenciador. Tenga en cuenta que los archivos de diseño no utilizados lo dicen en la arquitectura.

Recomendado:

Secuenciador de sección de ritmo MIDI Arduino: 8 pasos (con imágenes)

Secuenciador de sección de ritmo MIDI Arduino: Tener una buena caja de ritmos de software es fácil y barato hoy en día, pero usar un mouse mata la diversión para mí. Es por eso que me di cuenta de lo que inicialmente se pretendía como un secuenciador de batería MIDI de hardware puro de 64 pasos capaz de disparar hasta 12 elementos de batería diferentes

Sintetizador secuenciador paralelo: 17 pasos (con imágenes)

Sintetizador secuenciador paralelo: esta es una guía para crear un secuenciador simple. Un secuenciador es un dispositivo que produce cíclicamente una serie de pasos que luego impulsan un oscilador. Cada paso puede asignarse a un tono diferente y así crear secuencias o efectos de audio interesantes

Secuenciador simple: 16 pasos (con imágenes)

Secuenciador simple: una de las claves para hacer buena música es la repetición sin sentido. Para eso es genial el secuenciador simple. Hace lo mismo una y otra vez en una secuencia de ocho notas. Puede ajustar la frecuencia de la nota, la duración de la nota y

Consola Atari Punk con un secuenciador de 8 pasos para bebés: 7 pasos (con imágenes)

Consola Atari Punk con un secuenciador Baby 8 Step: esta construcción intermedia es la consola Atari Punk todo en uno y el secuenciador Baby 8 Step que puedes fresar en la fresadora de PCB de escritorio Bantam Tools. Se compone de dos placas de circuito: una es una placa de interfaz de usuario (UI) y la otra es una placa de utilidad

(casi) Programador universal MIDI SysEx CC (y secuenciador ): 7 pasos (con imágenes)

(casi) Programador Universal MIDI SysEx CC (y secuenciador …): a mediados de los ochenta, los fabricantes de sintetizadores comenzaron un programa de " menos es mejor " proceso que llevó a los sintetizadores barebones. Esto permitió la reducción de costos por parte del fabricante, pero hizo que el proceso de parcheo fuera tedioso, si no imposible, para el uso final